Compiling Parallel Algorithms to Memory Systems

Stephen A. Edwards

Columbia University

ESLsyn Keynote, June 2nd, 2012

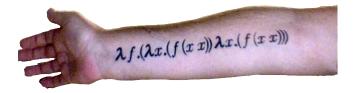

$(\lambda x.?)f = FPGA$

< □ > < 同 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ - 三 - のへぐ

▲□▶▲□▶▲□▶▲□▶ ▲□ ● ● ●

・ロト・国ト・モート ヨー・シタウ

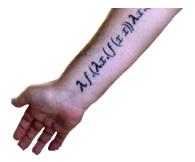

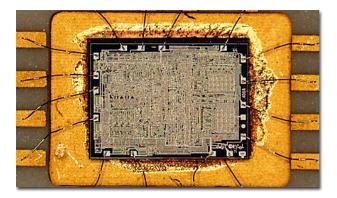

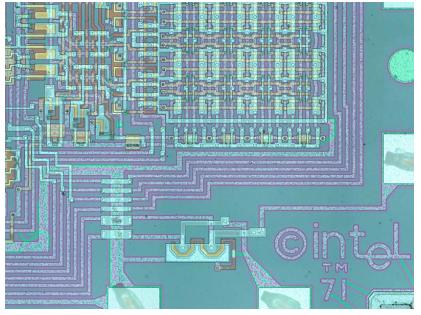

#### Moore's Law: Lots of Cheap Transistors...

"The complexity for minimum component costs has increased at a rate of roughly a factor of two per year."

Closer to every 24 months

Gordon Moore, *Cramming More Components onto Integrated Circuits*, Electronics, 38(8) April 19, 1965.

・ロト・日本・日本・日本・日本・日本

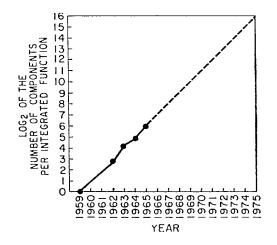

## Pollack's Rule: ...Give Diminishing Returns for Processors

Single-core processor performance follows the square root of area.

It takes  $4 \times$  the transistors to give  $2 \times$  the performance.

Fred J. Pollack, MICRO 1999 keynote. Graph from Borkar, DAC 2007

・ロト・西ト・ヨト・ヨト・ ヨー うへぐ

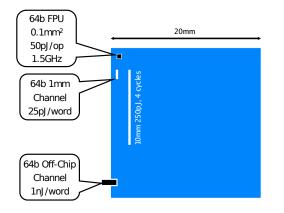

# Dally: Calculation is Cheap; Communication is Costly

"Chips are power limited and most power is spent moving data

Performance = Parallelism

▲□▶▲□▶▲□▶▲□▶ □ のQ@

Efficiency = Locality

Bill Dally's 2009 DAC Keynote, The End of Denial Architecture

## Parallelism for Performance and Locality for Efficiency

Dally: "Single-thread processors are in denial about these two facts"

We need different programming paradigms and different architectures on which to run them.

・ロト ・個ト ・ヨト ・ヨト ・ヨー

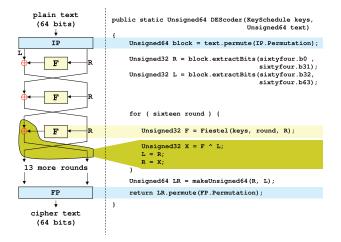

## Bacon et al.'s Liquid Metal

Fig. 2. Block level diagram of DES and Lime code snippet

JITting Lime (Java-like, side-effect-free, streaming) to FPGAs Huang, Hormati, Bacon, and Rabbah, *Liquid Metal*, ECOOP 2008.

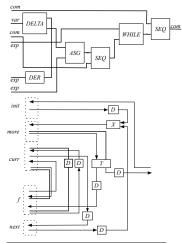

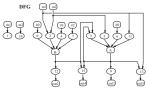

## Goldstein et al.'s Phoenix

Figure 3: C program and its representation comprising three hyperblocks; each hyperblock is shown as a numbered rectangle. The dotted lines represent predicate values. (This figure omits the token edges used for memory synchronization.)

Figure 8: Memory access network and implementation of the value and token forwarding network. The LOAD produces a data value consumed by the oval node. The STORE node may depend on the load (i.e., we have a token edge between the LOAD and the STORE, shown as a dashed line). The token travels to the root of the tree, which is a load-store queue (LSQ).

◆□▶ ◆□▶ ▲ □ ▶ ▲ □ ▶ ▲ □ ● ● ● ● ●

#### C to asynchronous logic, monolithic memory

Budiu, Venkataramani, Chelcea and Goldstein, Spatial Computation, ASPLOS 2004.

# Ghica et al.'s Geometry of Synthesis

Figure 1. In-place map schematic and implementation

Algol-like imperative language to handshake circuits Ghica, Smith, and Singh. *Geometry of Synthesis IV*, ICFP 2011

・ ロ ト ・ 雪 ト ・ 雪 ト ・ 目 ト

ъ

## Greaves and Singh's Kiwi

```

public static void SendDeviceID()

{ int device D = 0x76;

for (int i = 7; i > 0; i = -)

\{ scl = false; \}

sda_out = (deviceID \& 64) != 0;

Kiwi.Pause(); // Set it i-th bit of the device ID

scl = true; Kiwi.Pause(); // Pulse SCL

scl = false; deviceID = deviceID << 1;

Kiwi.Pause();

}

```

#### C# with a concurrency library to FPGAs

Greaves and Singh. Kiwi, FCCM 2008

< □ > < 同 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

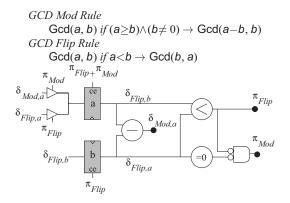

#### Arvind, Hoe et al.'s Bluespec

*Figure 1.3* Circuit for computing Gcd(*a*, *b*) from Example 1.

#### Guarded commands and functions to synchronous logic

Hoe and Arvind, Term Rewriting, VLSI 1999

・ ロ ト ・ 雪 ト ・ 雪 ト ・ 目 ト

3

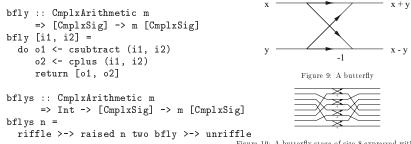

#### Sheeran et al.'s Lava

Figure 10: A butterfly stage of size 8 expressed with riffling

◆□▶ ◆□▶ ▲ □ ▶ ▲ □ ▶ ▲ □ ● ● ● ● ●

#### Functional specifications of regular structures

Bjesse, Claessen, Sheeran, and Singh. Lava, ICFP 1998

#### Kuper et al.'s $C\lambda aSH$

More operational Haskell specifications of regular structures

Baaij, Kooijman, Kuper, Boeijink, and Gerards. Chash, DSD 2010

・ロト・四ト・ヨト・ヨト ウタぐ

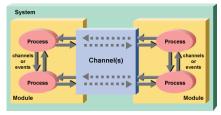

## AutoESL (Xilinx, was Cong's xPilot)

- ◆ SSDM (System-level Synthesis Data Model)

- Hierarchical netlist of concurrent processes and communication channels

- Each leaf process contains a sequential program which is represented by an extended LLVM IR with hardware-specific semantics

- · Port / IO interfaces, bit-vector manipulations, cycle-level notations

SystemC input; classical high-level synthesis for processes

Jason Cong, presentation at ISARS 2005

・ロト・一部・・ヨト・ヨト ヨー うらつ

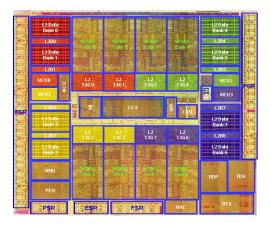

## Optimization of Parallel "Programs" Enables Chip Design

Sun's UltraSPARC T2 The "Niagara 2" 8 cores; 64 threads Built 2007, 1.6 GHz, 65 nm Released open-source as the OpenSPARC T2 www.opensparc.net

◆□▶ ◆□▶ ▲ □ ▶ ▲ □ ▶ ▲ □ ● ● ● ● ●

454 000 lines of synthesizable Verilog  $\rightarrow$  503 000 000 transistors *A mix of Boolean logic and structure*

#### The Lesson of Logic Synthesis: the Enabling Technology

How do you compile and optimize a digital logic circuit?

$$f_{1} = abcd + abce + a\overline{b}c\overline{d} + a\overline{b}\overline{c}\overline{d} + \overline{a}c + cdf + ab\overline{c}\overline{d}\overline{e} + a\overline{b}\overline{c}d\overline{f}$$

$$f_{2} = bdg + \overline{b}dfg + \overline{b}dg + b\overline{d}eg$$

$$f_1 = c(x + \overline{a}) + a\overline{cx}$$

$$f_2 = gx$$

$$x = d(b + f) + \overline{d}(\overline{b} + e)$$

#### The Lesson of Logic Synthesis: the Enabling Technology

How do you compile and optimize a digital logic circuit? Use a simple, formal model and automate it.

$$\begin{aligned} f_1 &= abcd + abce + a\overline{b}c\overline{d} + a\overline{b}\overline{c}\overline{d} + \overline{a}c + cdf + ab\overline{c}\overline{d}\overline{e} + a\overline{b}\overline{c}d\overline{f} \\ f_2 &= bdg + \overline{b}dfg + \overline{b}dg + b\overline{d}eg \\ & \text{Minimize} \end{aligned}$$

$$f_{1} = bcd + bce + \overline{bd} + \overline{a}c + cdf + ab\overline{c}\overline{d}\overline{e} + a\overline{b}\overline{c}d\overline{f}$$

$$f_{2} = bdg + dfg + \overline{bd}g + \overline{d}eg$$

Factor

$$f_1 = c \left( b(d+e) + \overline{b}(\overline{d}+f) + \overline{a} \right) + a\overline{c}(b\overline{d}\overline{e} + \overline{b}d\overline{f})$$

$$f_2 = g \left( d(b+f) + \overline{d}(\overline{b}+e) \right)$$

Decompose

$$f_1 = c(x + \overline{a}) + a\overline{cx}$$

$$f_2 = gx$$

$$x = d(b + f) + \overline{d}(\overline{b} + e)$$

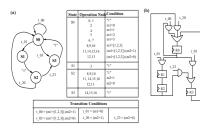

# High-Level Synthesis: Adding Time Meant Scheduling

Figure 2: (a) VHDL description; (b) Separate control and data-flow graphs

Bergamaschi, Behavioral Network Graph, DAC 1999.

Figure 3: (a) FSM for scheduled CFG in Figure 2(b), (b) Hardware implementation of FSM using one-hot encoding

・ロト・西ト・ヨト・ヨー シック・

## The High-Level Synthesis Lessons

#### Don't Start From C

"The so-called high-level specifications in reality grew out of the need for simulation and were often little more than an input language to make a discrete event simulator reproduce a specific behavior."

Gupta and Brewer, High-Level Synthesis: A Retrospective, 2008.

#### **Don't Forget Memory**

Goldstein et al.'s Phoenix synthesized asychronous hardware from ANSI C. Required heroic work [CGO 2003] to recover any parallelism.

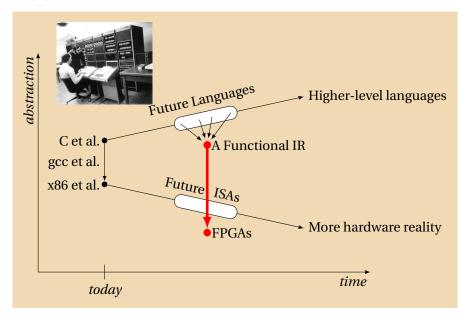

## Our Approach

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ - 三 - のへぐ

## **Our Approach**

## **Our Approach**

# Why Functional Specifications?

- Referential transparency/side-effect freedom make formal reasoning about programs vastly easier

- Inherently concurrent and race-free (Thank Church and Rosser). If you want races and deadlocks, you need to add constructs.

- Immutable data structures makes it vastly easier to reason about memory in the presence of concurrency

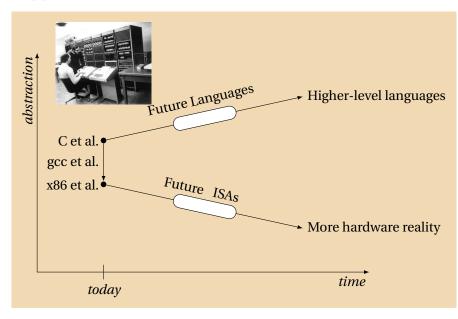

## Why FPGAs?

- We do not know the structure of future memory systems Homogeneous/Heterogeneous? Levels of Hierarchy? Communication Mechanisms?

- We do not know the architecture of future multi-cores

Programmable in Assembly/C?

Single- or multi-threaded?

Use FPGAs as a surrogate. Ultimately too flexible, but representative of the long-term solution.

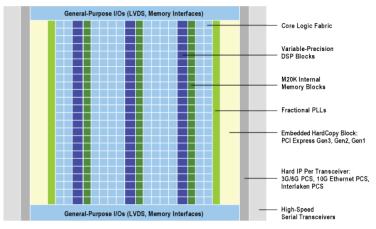

## A Modern High-End FPGA: Altera's Stratix V

2500 dual-ported 2.5KB 600 MHz memory blocks; 6 Mb total 350 36-bit 500 MHz DSP blocks (MAC-oriented datapaths) 300000 6-input LUTs; 28 nm feature size

・ロト・日本・ヨト・ヨー シック

## Let's Talk Details

◆□ ▶ ◆□ ▶ ◆ □ ▶ ◆ □ ▶ ◆ □ ● ◆ ○ ○ ○

## Let's Talk Details

#### Let's Talk Details

## **Our Starting Point: A Functional IR**

Inspired by the Glasgow Haskell Compiler's "Core" representation

$expr ::= name var^*$

Function call

< □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ <

Includes primitive arithmetic operators and type constructors

Non-tail-recursive calls generally inlined to improve parallelism; Mycroft and Sharp's [IWLS 2000] propose sharing policies

True recursion transformed to tail recursion with a stack

## **Our Starting Point: A Functional IR**

Inspired by the Glasgow Haskell Compiler's "Core" representation

$expr ::= name var^*$ | let  $(var = expr)^+$  in expr Function call Parallel evaluation

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ - 三里 - のへぐ

Parallelism and sequencing:

$\begin{array}{ccc} \mathbf{let} \ v_1 = e_1 & e_1 \\ v_2 = e_2 & e_2 \\ v_3 = e_3 \ \mathbf{in} \ e & e_3 \end{array} \right\} \text{ evaluated in parallel, then } e \\ \end{array}$

# **Our Starting Point: A Functional IR**

Inspired by the Glasgow Haskell Compiler's "Core" representation

```

expr ::= name var^*Function call| let (var = expr)^+ in exprParallel evaluation| case var of (pat -> expr)^+Multiway conditionalpat ::= literalExact match| _Default| Constr. (var | literal | _)^*Match a tagged union

```

Evaluate and return one of the expressions based on the pattern

ション (日本) (日本) (日本) (日本) (日本)

# **Our Starting Point: A Functional IR**

Inspired by the Glasgow Haskell Compiler's "Core" representation

```

expr ::= name var^*Function call| let (var = expr)^+ in exprParallel evaluation| case var of (pat -> expr)^+Multiway conditional| varVariable reference| literalLiteral valuepat ::= literalExact match| _Default| Constr. (var | literal | _)^*Match a tagged union

```

ション (日本) (日本) (日本) (日本) (日本)

# The Type System: Tagged Unions

Types are primitive (Boolean, Integer, etc.) or tagged unions:

type ::= TypeNamed type/primitive| Constr Type\* | ··· | Constr Type\*Tagged union

< □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ <

Subsume C structs, unions, and enums

Comparable power to C++ objects with virtual methods

Sometimes called "algebraic data types": sums of products

# The Type System: Tagged Unions

Types are primitive (Boolean, Integer, etc.) or tagged unions:

type ::= TypeNamed type/primitive| Constr Type\* | ··· | Constr Type\*Tagged union

**Examples:**

data Intlist = Nil -- Linked list of integers | Cons Int Intlist

data Bintree = Leaf Int -- Binary tree w/ integer leaves | Branch BinTree Bintree

data Expr = Literal Int

-- Arithmetic expression

| Var String

Binop Expr Op Expr

< □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ < □ ▶ <

data Op = Add | Sub | Mult | Div

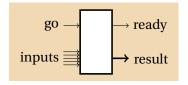

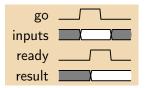

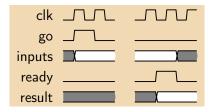

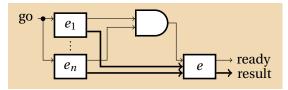

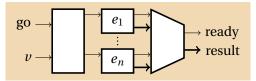

# Syntax-Directed Translation of Expressions to Hardware

### Combinational functions:

#### Sequential functions:

▲□▶▲□▶▲□▶▲□▶ □ のQの

### Translating Let and Case

Let makes all new variables available to its body.

Case invokes one of its sub-expressions, then synchronizes.

▲□▶▲□▶▲□▶▲□▶ □ のQ@

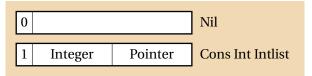

Representing Recursive Algebraic Data Types

Consider a list of integers:

data Intlist = Nil | Cons Int Intlist

An obvious representation:

- Usual byte-alignment unnecessary & wasteful in hardware

- Naturally stored & managed in a custom integer-list memory

- Width of pointer can depend on integer-list memory size

### Removing Recursion: Recursive Fibonacci Example

Starting point: a dumb way to compute Fibonacci numbers

▲□▶ ▲□▶ ▲ □▶ ▲ □▶ ▲ □ ● ● ● ●

$\begin{array}{l} fib \ 1 = 1 \\ fib \ 2 = 1 \\ fib \ n = fib \ (n-1) + fib \ (n-2) \end{array}$

## **Removing Recursion: Recursive Fibonacci**

### Reformatting

### **Removing Recursion: Continuation-Passing Style**

In continuation-passing style (the "and then?" transformation):

$$\begin{array}{rcl} fib1 & 1 & c & = & c & 1 \\ fib1 & 2 & c & = & c & 1 \\ fib1 & n & c & = & fib1 & (n-1) & & -- & Calls made sequential \\ & (\backslash n1 \rightarrow & fib1 & (n-2) & & -- & Intermediates named \\ & (\backslash n2 \rightarrow & c & (n1+n2))) & & -- & Add scheduled last \\ fib & n & = & fib1 & n & (\backslash x \rightarrow x) & & -- & Wrapper \end{array}$$

・ロト・(部・・ヨ・・ヨ・・ヨ・ のへぐ)

### **Removing Recursion: Naming Functions**

Naming functions; converting unbound variables to arguments:

$\begin{array}{rcl} fib1 & 1 & c & = & c & 1 \\ fib1 & 2 & c & = & c & 1 \\ fib1 & n & c & = & fib1 & (n-1) & (fib2 & n & c) & -- & \text{Unbound variables passed} \\ fib2 & n & c & n1 & = & fib1 & (n-2) & (fib3 & n1 & c) & -- & \text{Lambdas named} \\ fib3 & n1 & c & n2 & = & c & (n1 + n2) \\ fib & n & = & fib1 & n & fib0 \\ fib0 & n & = & n & & -- & \text{Identity function named} \end{array}$

< □ > < 同 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

### **Removing Recursion: True Recursion to Tail Recursion**

Introducing a stack; merging functions

-- Continuations (references to the lambda expressions)

data Stack = Fib2 Int Stack -- fib2 n c

| Fib3 Int Stack -- fib3 n1 c

| Fib0 -- identity function (bottom of stack)

# -- Invoke a named function or a continuation data Action = Fib Int -- fib n (outside call) | Fib1 Int Stack -- fib1 n c (recursive call) | Cont Stack Int -- c (...) (invoke continuation)

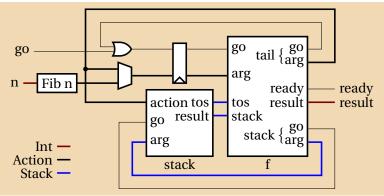

# Fibonacci Datapath

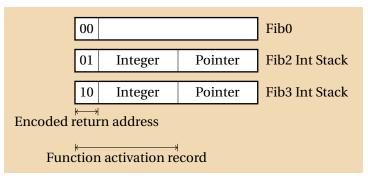

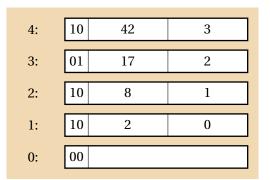

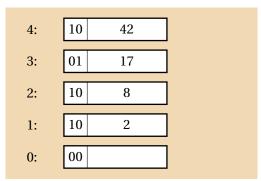

# Implementing the Stack in Hardware

```

This uses a list-like stack data type:

data Stack = Fib2 Int Stack

| Fib3 Int Stack

| Fib0

```

A naïve, but correct, way to implement it in hardware:

▲□▶▲□▶▲□▶▲□▶ □ のQ@

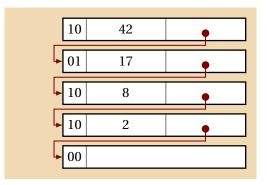

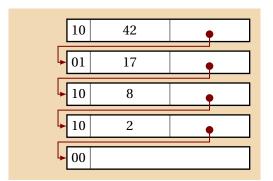

Fib3 42 (Fib2 17 (Fib3 8 (Fib3 2 Fib0)))

▲□▶▲□▶▲□▶▲□▶ ■ のへで

Fib3 42 (Fib2 17 (Fib3 8 (Fib3 2 Fib0)))

The only "pop" operation discards the previous top-of-stack f (Cont (Fib3 n1 c) n2) = f (Cont c (n1 + n2))

so this code will never generate a tree. Sequential memory allocation is safe.

Fib3 42 (Fib2 17 (Fib3 8 (Fib3 2 Fib0)))

Sequential memory allocation makes "next" pointers predictable ...

▲□▶▲□▶▲□▶▲□▶ □ のQ@

Fib3 42 (Fib2 17 (Fib3 8 (Fib3 2 Fib0)))

...so there is no need to store them.

Constructor (Fib0) always returns 0.

Constructors (Fib2/3 n s) writes (Fib2/3 n) at s + 1 and returns s + 1.

(ロ)

Reading 0 returns Fib0; reading *s* returns (Fib2/3 n s - 1).

# Specializing Data Types

Stacks are the tip of the iceberg

Synthesizing custom memory systems for specific types is a key goal of this project

Shape Analysis relevant here

This is a simple case; a simple, mathematical IR enables such clever optimizations.

▲□▶▲□▶▲□▶▲□▶ ▲□ ● のへで

Imagine trying to do this in C.

### Unrolling Code for Better Parallelism

$\begin{array}{l} fib \ 0 = 0 \\ fib \ 1 = 1 \\ fib \ n = fib \ (n-1) + fib \ (n-2) \end{array}$

*fib* (n-1) and *fib* (n-2) are functionally independent.

Yet because they share *fib*, they are performed sequentially.

< □ > < 同 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > <

### Unrolling Code for Better Parallelism

$fib \ 0 = 0$   $fib \ 1 = 1$   $fib \ n = fib' \ (n-1) + fib'' \ (n-2)$   $fib' \ 0 = 0$   $fib' \ 1 = 1$   $fib'' \ n = fib' \ (n-1) + fib' \ (n-2)$   $fib'' \ 0 = 0$   $fib'' \ 1 = 1$  $fib'' \ n = fib'' \ (n-1) + fib'' \ (n-2)$

By unrolling the recursion once, *fib*' and *fib*'' run in parallel.

A further improvement: balance the work done by *fib'* and *fib''*

・ロト・一部・・ヨト・ヨト ヨー うらつ

Unrolling Types for Better Locality

data Stack = Fib2 Int Stack | Fib3 Int Stack | Fib0

Each Stack object naturally represents a single activation record

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ - 三里 - のへぐ

Unrolling Types for Better Locality

data Stack = Fib2 Int Stack' | Fib3 Int Stack' | Fib0

data Stack' = Fib2 Int Stack'' | Fib3 Int Stack'' | Fib0

data Stack'' = Fib2 Int Stack''' | Fib3 Int Stack''' | Fib0

data Stack''' = Fib2 Int Stack | Fib3 Int Stack | Fib0 A similar unrolling amounts to packing records that can be processed in parallel

Abstract data types enables this

Imagine trying to do this safely in a C compiler

(ロ)

Example: Huffman Decoder in Haskell

data HTree = Branch HTree HTree | Leaf Char

decode :: HTree -> [Bool] -> [Char] -- Huffman tree & bitstream to symbols

decode table str = decoder table str

where

decoder (Leaf s) i = s : (decoder table i) -- Identified symbol; start again

decoder\_[] = []

decoder (Branch f\_) (False:xs) = decoder f xs -- 0: follow left branch

decoder (Branch\_t) (True:xs) = decoder t xs -- 1: follow right branch

< 日 > < 同 > < 目 > < 目 > < 目 > < 回 > < ○ < ○ </li>

Three data types: Input bitstream, output character stream, and Huffman tree

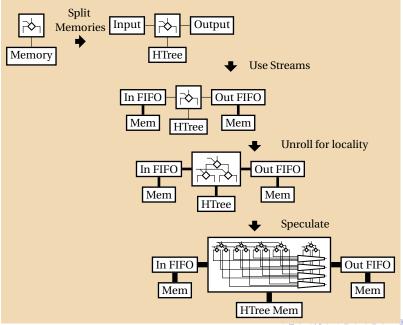

# Optimizations

# **Target Applications**

"Data-parallel irregular applications [that] manipulate large pointer-based data structures like graphs"

[Pingali et al.'s Galois project]

Datatype accelerators

Hash tables, Balanced trees, Heaps

Application-domain accelerators

Relational databases, Crypography, Data compression

Non-scientific computing: the stuff that's hard for vector units and GPGPUs

# Acknowledgements

Project started while at MSR Cambridge

Satnam Singh (now at Google) See his keynote tomorrow

Simon Peyton Jones (MSR)

Martha Kim (Columbia)