# Project RISCY

Shuai Zhang

#### RISC-V ISA

Open source ISA

Originated in UC Berkeley

Community maintained.

RISC-V: The Free and Open RISC Instruction Set Architecture

## Simple instruction set

Very few mandatory instructions

Easy to implement

Can expand to mult, fp, atomic, simd. etc

| 1 27 26 2             | 25 24 20 | 19 15 | 14 12  | 11 7        | 6 0    |    |

|-----------------------|----------|-------|--------|-------------|--------|----|

| funct7                | rs2      | rs1   | funct3 | rd          | opcode | R  |

| imm[1]                | [0:1     | rs1   | funct3 | rd          | opcode | I- |

| imm[11:5]             | rs2      | rs1   | funct3 | imm[4:0]    | opcode | S- |

| imm[12 10:5]          | rs2      | rs1   | funct3 | imm[4:1 11] | opcode | В  |

| imm[31:12]            |          |       |        | rd          | opcode | U  |

| imm[20]10:1[11]19:12] |          |       |        | rd          | opcode | J- |

#### RV32I Base Instruction Set

|              | imm[31:12]        | rd  | 0110111 | LUI         |         |        |

|--------------|-------------------|-----|---------|-------------|---------|--------|

|              | imm[31:12]        | rd  | 0010111 | AUIPC       |         |        |

|              | imm[20 10:1 11 19 |     |         | rd          | 1101111 | JAL    |

| imm[1        | 1:0]              | rs1 | 000     | rd          | 1100111 | JALR   |

| imm[12 10:5] | rs2               | rs1 | 000     | imm[4:1 11] | 1100011 | BEQ    |

| imm[12 10:5] | rs2               | rs1 | 001     | imm[4:1 11] | 1100011 | BNE    |

| imm[12 10:5] | rs2               | rs1 | 100     | imm[4:1 11] | 1100011 | BLT    |

| imm[12 10:5] | rs2               | rs1 | 101     | imm[4:1 11] | 1100011 | BGE    |

| imm[12 10:5] | rs2               | rs1 | 110     | imm[4:1]11] | 1100011 | BLTU   |

| imm[12 10:5] | rs2               | rs1 | 111     | imm[4:1 11] | 1100011 | BGEU   |

| imm[1        |                   | rs1 | 000     | rd          | 0000011 | LB     |

|              | imm[11:0]         |     | 001     | rd          | 0000011 | LH     |

| imm[1        |                   | rs1 | 010     | rd          | 0000011 | LW     |

| imm[1        |                   | rs1 | 100     | rd          | 0000011 | LBU    |

| imm[1        | 1:0]              | rs1 | 101     | rd          | 0000011 | LHU    |

| imm[11:5]    | rs2               | rs1 | 000     | imm[4:0]    | 0100011 | SB     |

| imm[11:5]    | rs2               | rs1 | 001     | imm[4:0]    | 0100011 | SH     |

| imm[11:5]    | rs2               | rs1 | 010     | imm[4:0]    | 0100011 | SW     |

| imm 1        | 1:0]              | rs1 | 000     | rd          | 0010011 | ADDI   |

| imm 1        | imm[11:0]         |     | 010     | rd          | 0010011 | SLTI   |

| imm 1        | imm[11:0]         |     | 011     | rd          | 0010011 | SLTIU  |

| imm 1        | imm[11:0]         |     | 100     | rd          | 0010011 | XORI   |

| imm[1        | imm[11:0]         |     | 110     | rd          | 0010011 | ORI    |

| imm 1        | imm[11:0]         |     | 111     | rd          | 0010011 | ANDI   |

| 0000000      | shamt             | rs1 | 001     | rd          | 0010011 | SLLI   |

| 0000000      | shamt             | rs1 | 101     | rd          | 0010011 | SRLI   |

| 0100000      | shamt             | rs1 | 101     | rd          | 0010011 | SRAI   |

| 0000000      | rs2               | rs1 | 000     | rd          | 0110011 | ADD    |

| 0100000      | rs2               | rs1 | 000     | rd          | 0110011 | SUB    |

| 0000000      | rs2               | rs1 | 001     | rd          | 0110011 | SLL    |

| 0000000      | rs2               | rs1 | 010     | rd          | 0110011 | SLT    |

| 0000000      | rs2               | rs1 | 011     | rd          | 0110011 | SLTU   |

| 0000000      | rs2               | rs1 | 100     | rd          | 0110011 | XOR    |

| 0000000      | rs2               | rs1 | 101     | rd          | 0110011 | SRL    |

| 0100000      | rs2               | rs1 | 101     | rd          | 0110011 | SRA    |

| 0000000      | rs2               | rs1 | 110     | rd          | 0110011 | OR     |

| 0000000      | rs2               | rs1 | 111     | rd          | 0110011 | AND    |

| fm p         | red succ          | rs1 | 000     | rd          | 0001111 | FENCE  |

|              | 00000000000       |     | 000     | 00000       | 1110011 | ECALL  |

| 0000000      | 00000000001       |     | 000     | 00000       | 1110011 | EBREAK |

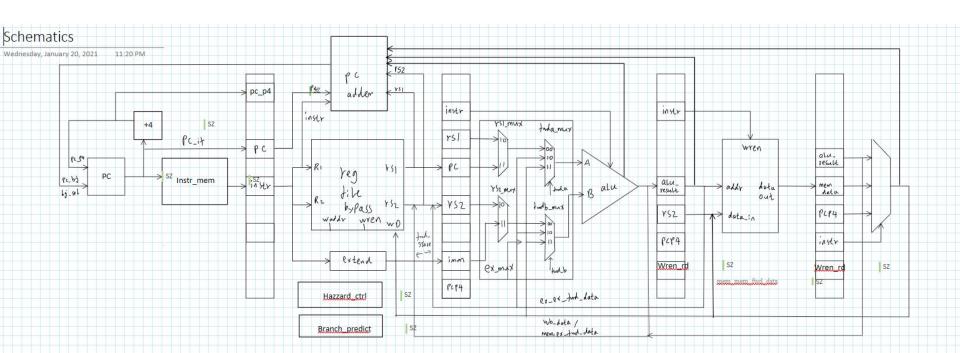

### Classic 5 stage pipeline

Also instruction buffer