# CSEE 4840 Embedded System Design Final Project Report

# **Convolutional Neural Network**

## 1. Introduction

Convolutional Neural Network (CNN) is widely used in the machine learning task in the computer vision and neural language processing area. In this project, we implement the convolutional neural network algorithm on the DE-1 SOC FPGA + HPS to run a pre-trained CNN-based network: VGG-11.

## 2. Data Flow

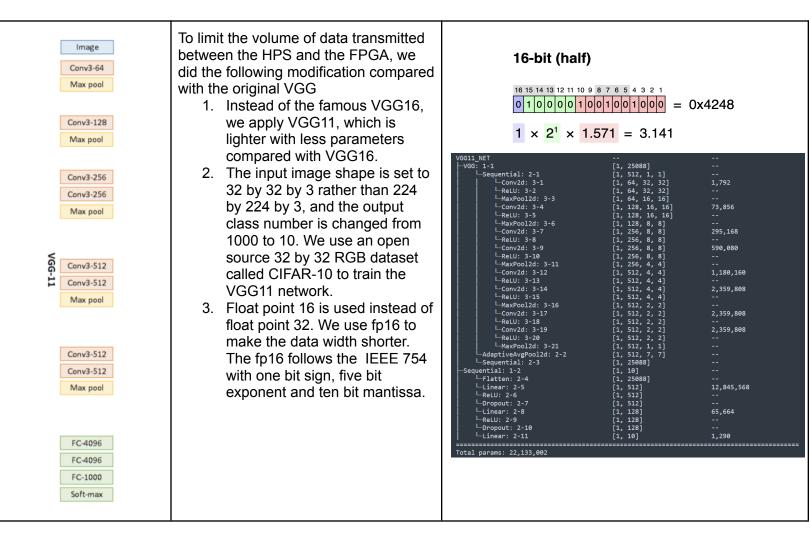

The figure below shows the structure of the VGG11, which contains these types of operator: conv2d, Relu, max pooling 2d, adaptive average pooling, linear(fully connection).

# 3. Hardware System Architecture

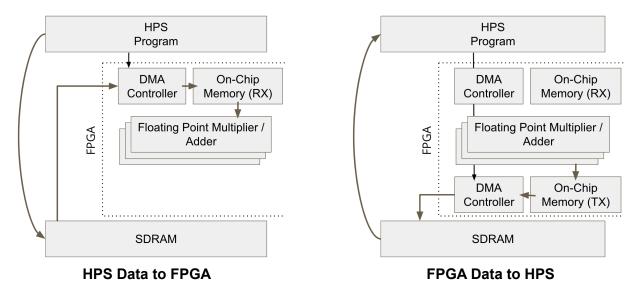

The system is built with two main components, HPS and FPGA that work with each other. From high level, the HPS is in charge of interfacing with the user and obtains the initial data, whereas the FPGA is in charge of low level computations.

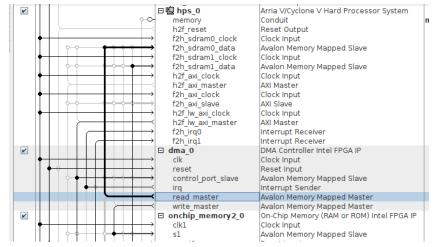

The system is first configured and generated using qsys (platform designer). The qsys configuration is as follows:

## Columbia University Spring 2022

|              | Connections                                                                                                                                                     | Name                                | Description<br>Clock Source                                              | Export                                           | Clock                       | Base            | End         | IRQ         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------|-----------------------------|-----------------|-------------|-------------|

|              | D-                                                                                                                                                              | clk_in                              | Clock Input                                                              | clk                                              | exported                    |                 |             |             |

| 0            |                                                                                                                                                                 | clk_in_reset                        | Reset Input                                                              | reset                                            | -                           |                 |             |             |

|              |                                                                                                                                                                 | clk<br>clk_reset                    | Clock Output<br>Reset Output                                             | Double-click to export<br>Double-click to export | clk_0                       |                 |             |             |

|              |                                                                                                                                                                 | ⊟ III hps_0                         | Arria V/Cyclone V Hard Processor System                                  |                                                  |                             |                 |             |             |

|              | <u> </u>                                                                                                                                                        | memory<br>h2f reset                 | Conduit<br>Reset Output                                                  | memory<br>Double-click to export                 |                             |                 |             |             |

| ++-          | (                                                                                                                                                               | f2h_sdram0_clock                    | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

|              |                                                                                                                                                                 | f2h_sdram0_data                     | Avalon Memory Mapped Slave                                               | Double-click to export                           | [f2h_sdram0_clock]          | = 0x0000_0000   | Oxffff_fff  |             |

|              | · · · · · · · · · · · · · · · · · · ·                                                                                                                           | f2h_sdram1_clock<br>f2h_sdram1_data | Clock Input<br>Avalon Memory Mapped Slave                                | Double-click to export<br>Double-click to export | clk_0<br>[f2h_sdram1_clock] | = 0x0000_0000   | 0xffff_ffff |             |

| •            | $\rightarrow$                                                                                                                                                   | h2f_axi_clock                       | Clock Input                                                              | Double-click to export                           | clk_0                       | - 0x0000_0000   | 0,1111_1111 |             |

|              |                                                                                                                                                                 | h2f_axi_master                      | AXI Master                                                               | Double-click to export                           | [h2f_axi_clock]             |                 |             |             |

|              | · · · · · · · · · · · · · · · · · · ·                                                                                                                           | f2h_axi_clock<br>f2h_axi_slave      | Clock Input<br>AXI Slave                                                 | Double-click to export<br>Double-click to export | clk_0<br>[f2h_axi_clock]    | -               |             |             |

| +            |                                                                                                                                                                 | h2f_lw_axi_clock                    | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

|              |                                                                                                                                                                 | h2f_lw_axi_master                   | AXI Master                                                               | Double-click to export                           | [h2f_lw_axi_clock]          | 700             |             |             |

|              |                                                                                                                                                                 | f2h_irq0<br>f2h_irq1                | Interrupt Receiver<br>Interrupt Receiver                                 | Double-click to export<br>Double-click to export |                             | IRQ<br>IRQ      |             |             |

|              |                                                                                                                                                                 | 🗆 dma_0                             | DMA Controller Intel FPGA IP                                             |                                                  |                             |                 |             |             |

|              |                                                                                                                                                                 | clk                                 | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

|              | $\land \bullet \bullet$ | reset<br>control_port_slave         | Reset Input<br>Avalon Memory Mapped Slave                                | Double-click to export<br>Double-click to export | [clk]<br>[clk]              | ■ 0x0000_0000   | 0x0000_001f |             |

|              |                                                                                                                                                                 | irq                                 | Interrupt Sender                                                         | Double-click to export                           | [clk]                       |                 | 0.0000_0011 | <u>⊢</u> ₫- |

|              |                                                                                                                                                                 | read_master                         | Avalon Memory Mapped Master                                              | Double-click to export                           | [clk]                       |                 |             |             |

|              |                                                                                                                                                                 | write_master<br>onchip_memory2_0    | Avalon Memory Mapped Master<br>On-Chip Memory (RAM or ROM) Intel FPGA IP | Double-click to export                           | [clk]                       |                 |             |             |

|              | $\rightarrow$                                                                                                                                                   | clk1                                | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

|              |                                                                                                                                                                 | sl                                  | Avalon Memory Mapped Slave                                               | Double-click to export                           | [clk1]                      | = 0x0000        | 0x0fff      |             |

|              | ,                                                                                                                                                               | resetl<br>s2                        | Reset Input<br>Avalon Memory Mapped Slave                                | Double-click to export<br>onchip_memory2_0_s2    | [clk1]<br>[clk2]            | <b>₽</b>        |             |             |

|              | $\rightarrow$                                                                                                                                                   | clk2                                | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

|              | $\diamond + + + + + + \rightarrow$                                                                                                                              | reset2                              | Reset Input                                                              | Double-click to export                           | [clk2]                      |                 |             |             |

|              |                                                                                                                                                                 | onchip_memory2_1                    | On-Chip Memory (RAM or ROM) Intel FPGA IP                                |                                                  |                             |                 |             |             |

| +            | $\rightarrow$                                                                                                                                                   | clk1                                | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

|              |                                                                                                                                                                 | sl<br>resetl                        | Avalon Memory Mapped Slave<br>Reset Input                                | onchip_memory2_1_s1<br>Double-click to export    | [clk1]<br>[clk1]            |                 |             |             |

|              | $\diamond$                                                                                                                                                      | s2                                  | Avalon Memory Mapped Slave                                               | Double-click to export                           | [clk2]                      | <i>≕</i> 0x0000 | OxOfff      |             |

| +            | $\rightarrow$                                                                                                                                                   | clk2                                | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

| 1            |                                                                                                                                                                 | reset2<br>dma_1                     | Reset Input<br>DMA Controller Intel FPGA IP                              | Double-click to export                           | [clk2]                      |                 |             |             |

| ♦ -   -      |                                                                                                                                                                 | clk                                 | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

| ♦→           | $\rightarrow$                                                                                                                                                   | reset                               | Reset Input                                                              | Double-click to export                           | [clk]                       |                 |             |             |

|              |                                                                                                                                                                 | control_port_slave<br>irq           | Avalon Memory Mapped Slave<br>Interrupt Sender                           | Double-click to export<br>Double-click to export | [clk]<br>[clk]              |                 | 0x0000_003f | ,<br>→ lo   |

|              | $\square$                                                                                                                                                       | read_master                         | Avalon Memory Mapped Master                                              | Double-click to export                           | [clk]                       |                 |             |             |

|              |                                                                                                                                                                 | write_master                        | Avalon Memory Mapped Master                                              | Double-click to export                           | [clk]                       |                 |             |             |

|              |                                                                                                                                                                 | image_sent_ocm<br>clk               | PIO (Parallel I/O) Intel FPGA IP<br>Clock Input                          | Double-click to export                           | clk_0                       |                 |             |             |

| II ₩         |                                                                                                                                                                 | reset                               | Reset Input                                                              | Double-click to export<br>Double-click to export | [clk]                       |                 |             |             |

|              | $\diamond \bullet \bullet \bullet \bullet \bullet \rightarrow$                                                                                                  | sl                                  | Avalon Memory Mapped Slave                                               | Double-click to export                           | [clk]                       | e 0x0000_0040   | 0x0000_004f |             |

|              | ~~                                                                                                                                                              | external_connection                 | Conduit                                                                  | image_sent_ocm                                   |                             |                 |             |             |

|              |                                                                                                                                                                 | fpga_stat<br>clk                    | PIO (Parallel I/O) Intel FPGA IP<br>Clock Input                          | Double-click to export                           | clk_0                       |                 |             |             |

| 🔶            | + + + + + + + + + + + + + + + + + + +                                                                                                                           | reset                               | Reset Input                                                              | Double-click to export                           | [clk]                       |                 |             |             |

|              |                                                                                                                                                                 | sl<br>external connection           | Avalon Memory Mapped Slave                                               | Double-click to export                           | [clk]                       |                 | 0x0000_005f |             |

|              |                                                                                                                                                                 | external_connection h2f_start       | Conduit<br>PIO (Parallel I/O) Intel FPGA IP                              | fpga_stat                                        |                             |                 |             |             |

| +            |                                                                                                                                                                 | clk                                 | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

| <b>†</b>     |                                                                                                                                                                 | reset<br>sl                         | Reset Input<br>Avalan Memory Manped Slave                                | Double-click to export                           | [clk]<br>[clk]              |                 | 0x0000 006f |             |

|              |                                                                                                                                                                 | si<br>external_connection           | Avalon Memory Mapped Slave<br>Conduit                                    | Double-click to export<br>h2f_start              | [cik]                       | 00000_0000      | 0x0000_0001 |             |

|              |                                                                                                                                                                 | f2h_start                           | PIO (Parallel I/O) Intel FPGA IP                                         | _                                                |                             |                 |             |             |

|              |                                                                                                                                                                 | clk                                 | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

| II TÎ        |                                                                                                                                                                 | reset<br>sl                         | Reset Input<br>Avalon Memory Mapped Slave                                | Double-click to export<br>Double-click to export | [clk]<br>[clk]              | = 0x0000_0070   | 0x0000_007f |             |

|              |                                                                                                                                                                 | external_connection                 | Conduit                                                                  | f2h_start                                        |                             |                 |             |             |

|              |                                                                                                                                                                 | D hof finish                        | BIO (Barallal I/O) Intel 50.04 ID                                        | -                                                |                             |                 |             |             |

| ++-          | ,                                                                                                                                                               | h2f_finish<br>clk                   | PIO (Parallel I/O) Intel FPGA IP<br>Clock Input                          | Double-click to export                           | clk_0                       |                 |             |             |

| +            | • • • • • • • • • • • • • • • • • • •                                                                                                                           | reset                               | Reset Input                                                              | Double-click to export                           | [clk]                       |                 |             |             |

|              |                                                                                                                                                                 | sl<br>external connection           | Avalon Memory Mapped Slave                                               | Double-click to export                           | [clk]                       | = 0x0000_0080   | 0x0000_008f |             |

|              |                                                                                                                                                                 | external_connection  f2h_finish     | Conduit<br>PIO (Parallel I/O) Intel FPGA IP                              | h2f_finish                                       |                             |                 |             |             |

| ++-          | · · · · · · · · · · · · · · · · · · ·                                                                                                                           | clk                                 | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

|              |                                                                                                                                                                 | reset<br>sl                         | Reset Input<br>Avalon Memory Mapped Slave                                | Double-click to export<br>Double-click to export | [clk]<br>[clk]              |                 | 0x0000_009f |             |

|              | 00                                                                                                                                                              | external_connection                 | Conduit                                                                  | f2h_finish                                       | [CIV]                       | 0000_0090       | 0000_0091   |             |

|              |                                                                                                                                                                 | h2f_read_length                     | PIO (Parallel I/O) Intel FPGA IP                                         | -                                                |                             |                 |             |             |

| 1            | · · · · · · · · · · · · · · · · · · ·                                                                                                                           | clk<br>reset                        | Clock Input<br>Reset Input                                               | Double-click to export<br>Double-click to export | clk_0<br>[clk]              |                 |             |             |

|              |                                                                                                                                                                 | sl                                  | Avalon Memory Mapped Slave                                               | Double-click to export<br>Double-click to export | [clk]                       | = 0x0000_0100   | 0x0000_010f |             |

|              | ·•                                                                                                                                                              | external_connection                 | Conduit                                                                  | h2f_read_length                                  |                             |                 | _           |             |

|              |                                                                                                                                                                 | f2h_write_length<br>clk             | PIO (Parallel I/O) Intel FPGA IP<br>Clock Input                          | Double-click to export                           | clk_0                       |                 |             |             |

| ↓            | • <b>                                    </b>                                                                                                                   | reset                               | Reset Input                                                              | Double-click to export                           | [clk]                       |                 |             |             |

|              |                                                                                                                                                                 | sl                                  | Avalon Memory Mapped Slave                                               | Double-click to export                           | [clk]                       | = 0x0000_0110   | 0x0000_011f |             |

|              | 00                                                                                                                                                              | external_connection h2f_buf_offset  | Conduit<br>PIO (Parallel I/O) Intel FPGA IP                              | f2h_write_length                                 |                             |                 |             |             |

| +            |                                                                                                                                                                 | clk                                 | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

| •            | • • • • • • • • • • • • • • • • • • •                                                                                                                           | reset                               | Reset Input                                                              | Double-click to export                           | [clk]                       |                 |             |             |

|              |                                                                                                                                                                 | sl<br>ovternal connection           | Avalon Memory Mapped Slave                                               | Double-click to export                           | [clk]                       | = 0x0000_0120   | 0x0000_012f |             |

|              | $\land$                                                                                                                                                         | external_connection  f2h buf offset | Conduit<br>PIO (Parallel I/O) Intel FPGA IP                              | h2f_buf_offset                                   |                             |                 |             |             |

|              | $  +   +   +   +   \rightarrow$                                                                                                                                 | clk                                 | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

|              | + 1 + + + + + + + + + + + + + + + + +                                                                                                                           | reset                               | Reset Input                                                              | Double-click to export                           | [clk]                       |                 | 0.0000 0000 |             |

|              |                                                                                                                                                                 | s1<br>external_connection           | Avalon Memory Mapped Slave<br>Conduit                                    | Double-click to export<br>f2h_buf_offset         | [clk]                       | = 0x0000_0130   | 0x0000_013f |             |

|              |                                                                                                                                                                 | ■ feat_map_dim                      | PIO (Parallel I/O) Intel FPGA IP                                         | izi_bui_onset                                    |                             |                 |             |             |

| an 1 - 1 - 1 |                                                                                                                                                                 | clk                                 | Clock Input                                                              | Double-click to export                           | clk_0                       |                 |             |             |

| •            |                                                                                                                                                                 |                                     | Reset Input                                                              | Double-click to export                           | [clk]                       |                 |             |             |

| •            |                                                                                                                                                                 | reset<br>sl                         | Avalon Memory Mapped Slave                                               | Double-click to export                           | [clk]                       |                 | 0x0000_014f |             |

The detailed configuration of each block is as follows:

The HPS system is configured with two DDR3 SDRAM interfaces, connected through the Avalon Memory Mapped interface as shown below. One is configured to read-only and the other as write-only.

| * AXI Bridges              |                    |          |          |              |

|----------------------------|--------------------|----------|----------|--------------|

| FPGA-to-HPS interface v    | 64-bit             | •        |          |              |

| HPS-to-FPGA interface v    | 64-bit             | •        |          |              |

| Lightweight HPS-to-FPG     | A interface width: | 32-bit   | •        |              |

| * FPGA-to-HPS SDRAM        | Interface          |          |          |              |

| Click the '+' and '-' butt | ons to add and re  | move FPG | A-to-HPS | SDRAM ports. |

| Name                       | Туре               |          | Width    |              |

| f2h sdram0                 | Avalon-MM Rea      | d-Only   | 32       |              |

| f2h_sdram1                 | Avalon-MM Writ     | te-Only  | 32       |              |

|                            |                    |          |          |              |

|                            |                    |          |          |              |

|                            |                    |          |          |              |

|                            |                    |          |          |              |

Two DMA-onchip\_memory pairs are created for exchanging data between HPS and FPGA. As seen below, the first dma0 has its read\_master connected to HPS's sdram0 (read-only), and write\_master to onchip\_memory0. This dma copies data from HPS to the onchip\_memory. Vise versa, dma1 has its read\_master connected to on chip memory1 and write master connected to HPS's sdram1 (write-only).

- A list of PIO IP cores are added for HPS to send or receive control signals from / to FPGA. As seen below, the h2f\_finish signal has one bit and is configured as an input, with conduit "h2f\_finish" and base address 0x0000080.

| + Use Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Name                                                        | Description                                                                  | Export                 | Clock | Base          | End           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------|------------------------|-------|---------------|---------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | > sl                                                        | Avalon Memory Mapped Slave                                                   | Double-click to export | [clk] |               | 0x0000_007f   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | external_connection                                         | Conduit                                                                      | f2h_start              |       |               |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | h2f_finish                                                  | PIO (Parallel I/O) Intel FPGA IP                                             |                        |       |               |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | → clk                                                       | Clock Input                                                                  | Double-click to export | clk_0 |               |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | reset                                                       | Reset Input                                                                  | Double-click to export | [clk] |               |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | sl                                                          | Avalon Memory Mapped Slave                                                   | Double-click to export | [clk] | © 0x0000_0080 | 0x0000_008f   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>external_connection</li> <li>f2h finish</li> </ul> | Conduit<br>PIO (Parallel I/O) Intel FPGA IP                                  | h2f_finish             |       |               |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | → clk                                                       | Clock Input                                                                  | Double-click to export | clk_0 |               |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             | clock input                                                                  | Bouble click to export |       |               |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             | PIO (Parallel I/O) Intel FPGA IP - I                                         | of finish              |       |               | 🚫 009f        |

| PIO (Parallel I/O) Intel FPG<br>altera_avalon_pio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A IP                                                        |                                                                              | 21_110150              |       | Document      |               |

| Core altera_avalori_pio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |                                                                              | 2f_mnsn                |       | Document      |               |

| llock Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Basic Se                                                    | ttings                                                                       | zr_misn                |       | Document      | ation         |

| lock Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Basic Se<br>Width (1-3                                      | ttings<br>12 bits): 1                                                        | 21_IMISN               |       | Document      | ation         |

| lock Diagram<br>Show signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Basic Se                                                    | ttings                                                                       | 21_IMISN               |       | Document      | ation         |

| lock Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Basic Se<br>Width (1-3                                      | ttings<br>2 bits): <u>1</u><br>O Bidir                                       | 21_IMISN               |       | Document      | ation         |