Processors, FPGAs, and ASICs Part 2: Processors to Fixed-Function

Stephen A. Edwards

**Columbia University**

Spring 2020

| Spectrum of IC choices<br>Flexible, efficient You choose |                       |                                |  |  |

|----------------------------------------------------------|-----------------------|--------------------------------|--|--|

| Flexible, e                                              | mcient                | You choose                     |  |  |

|                                                          | Full Custom           | Polygons (Intel)               |  |  |

|                                                          |                       |                                |  |  |

|                                                          | ASIC                  | Circuit (Sony)                 |  |  |

|                                                          | Gate Array            | Wires                          |  |  |

|                                                          |                       |                                |  |  |

|                                                          | FPGA                  | Logic network                  |  |  |

|                                                          | PLD                   | Logic function                 |  |  |

|                                                          | GP Processor          | Program (e.g., ARM)            |  |  |

|                                                          | SP Processor          | Program (e.g., DSP)            |  |  |

|                                                          | Multifunction         | Settings (e.g., Accelerometer) |  |  |

|                                                          | <b>Fixed-function</b> | Part number (e.g., 7400)       |  |  |

| Cheap, quick to design                                   |                       |                                |  |  |

### **Euclid's Algorithm**

```

int gcd(int m, int n)

{

int r;

while ((r = m % n) != 0) {

m = n;

n = r;

}

return n;

}

```

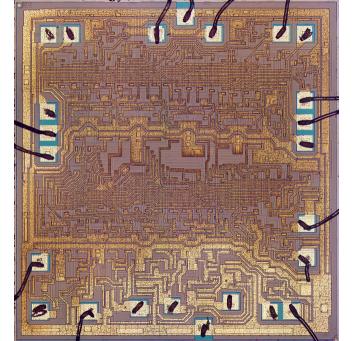

The Intel 80386 c. 1985

### i386 Programmer's Model

| 31 |     | 0 |

|----|-----|---|

|    | eax |   |

|    | ebx |   |

|    | ecx |   |

|    | edx |   |

Mostly General-Purpose Registers

| esi |

|-----|

| edi |

| ebp |

| esp |

Source index Destination index Base pointer Stack pointer

| 15 |  |

|----|--|

|----|--|

0

| CS |  |

|----|--|

| ds |  |

| SS |  |

| es |  |

| fs |  |

| gs |  |

Code segment Data segment Stack segment Extra segment Data segment Data segment

| eflags |  |

|--------|--|

| eip    |  |

Status word Instruction Pointer

## Euclid on the i386

```

int gcd(int m, int n)

{

int r;

while ((r = m % n) != 0) {

m = n;

n = r;

}

return n;

}

```

gcd: pushl %ebp movl %esp,%ebp pushl %ebx movl 8(%ebp),%eax movl 12(%ebp),%ecx jmp .L6 .L4: movl %ecx,%eax movl %ebx.%ecx .L6: cltd idivl %ecx movl %edx,%ebx testl %edx,%edx jne .L4 movl %ecx.%eax movl -4(%ebp),%ebx leave ret

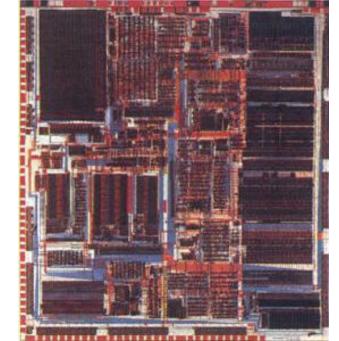

Sun's SPARC Processor c. 1987

## SPARC Programmer's Model

| 31     | 0 |                  | 31    | 0 |                 |

|--------|---|------------------|-------|---|-----------------|

| r0     |   | Always 0         | r16/l | 0 | Local Registers |

| r1     |   | Global Registers | r17/l | 1 |                 |

| i      |   |                  | i     |   |                 |

| r7     |   |                  | r23/l | 7 |                 |

| r8/o0  |   | Output Registers | r24/i | 0 | Input Registers |

| i      |   | <i>.</i>         | :     |   |                 |

| r14/o6 |   | Stack Pointer    | r30/i | 6 | Frame Pointer   |

| r15/o7 |   |                  | r31/i | 7 | Return Address  |

|        |   | -                |       |   |                 |

| PSR |

|-----|

| PC  |

| nPC |

Status Register Program Counter Next PC

## **SPARC Register Windows**

The output registers of the calling procedure become the inputs to the called procedure

The global registers remain unchanged

The local registers are not visible across procedures

|        |        | r8/o0  |

|--------|--------|--------|

|        |        | :      |

|        |        | r15/o7 |

|        |        | r16/l0 |

|        |        | :      |

|        |        | r23/l7 |

|        | r8/o0  | r24/i0 |

|        | :      | :      |

|        | r15/o7 | r31/i7 |

|        | r16/l0 |        |

|        | :      |        |

|        | r23/l7 |        |

| r8/o0  | r24/i0 |        |

| :      | :      |        |

| r15/o7 | r31/i7 |        |

| r16/l0 |        |        |

| :      |        |        |

| r23/l7 |        |        |

| r24/i0 |        |        |

| :      |        |        |

| r31/i7 |        |        |

### Euclid on the SPARC

```

int gcd(m, n)

int m, n;

int r;

while ((r = m \% n) != 0) {

m = n;

n = r;

}

return n:

```

| -    |         |                 |

|------|---------|-----------------|

| gcd: | save    | %sp,-96,%sp     |

|      | mov     | %i0,%o0         |

|      | call    | . <b>rem</b> ,2 |

|      | mov     | %i1,%o1         |

|      | mov     | %00,%i5         |

|      | tst     | %i5             |

|      | be      | L2              |

|      | mov     | %i1,%o0         |

| L1:  | mov     | %i5,%i1         |

|      | call    | . <b>rem</b> ,2 |

|      | mov     | %i1,%o1         |

|      | mov     | %00,%i5         |

|      | tst     | %i5             |

|      | bne,a   | L1              |

|      | mov     | %i1,%o0         |

| L2:  | ret     |                 |

|      | restore | %g0,%i1,%o0     |

|      |         |                 |

# Motorola's DSP56000 c. 1986

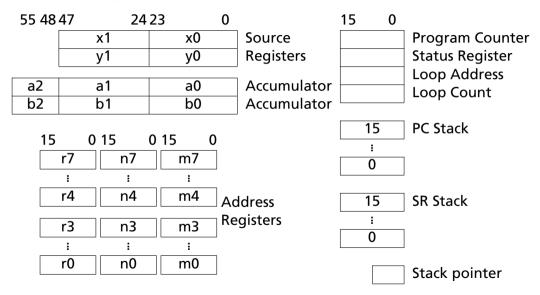

### DSP 56000 Programmer's Model

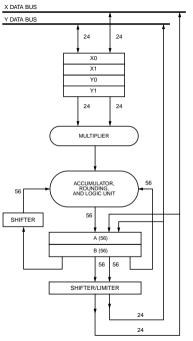

## Motorola DSP56000 Data ALU

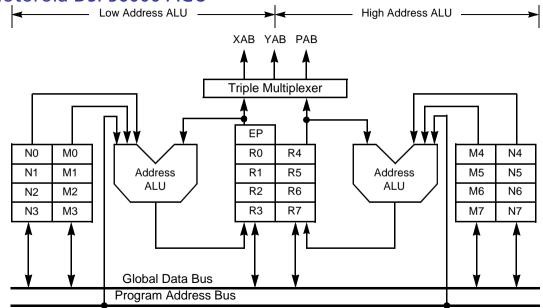

Motorola DSP56000 AGU

### FIR Filter in 56000

```

move #samples, r0

move #coeffs, r4

move \#n-1, mO

move mO. m4

movep y:input, x:(r0)

clr a x:(r0)+, x0 y:(r4)+, v0

rep

#n-1

mac x0,v0,a x:(r0)+, x0 y:(r4)+, v0

macr x0, y0, a (r0)-

movep a, y:output

```

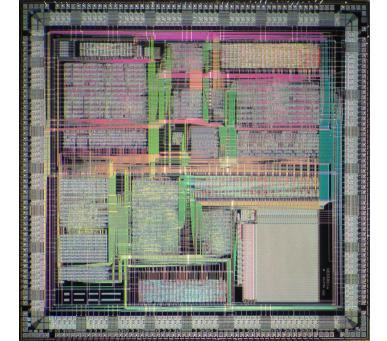

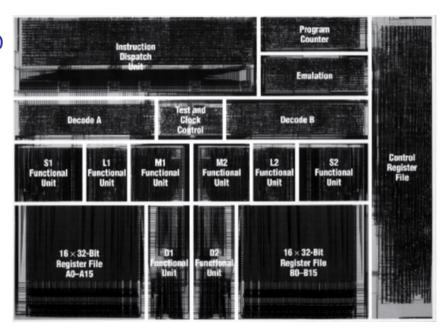

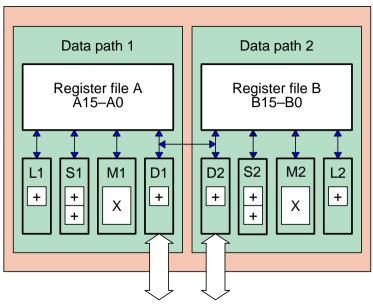

TI TMS320 C6201 VLIW DSP c. 1997

TI TMS320 C6000 VLIW DSP

Dual 32-bit load/store path

### FIRLOOP:

|      | LDH | .D1  | *A1++, A2  | ; | Fetch next sample      |

|------|-----|------|------------|---|------------------------|

|      | LDH | .D2  | *B1++, B2  | ; | Fetch next coefficient |

| [B0] | SUB | .L2  | BO, 1, BO  | ; | Decrement loop count   |

| [B0] | В   | .S2  | FIRLOOP    | ; | Branch if non-zero     |

|      | MPY | .M1X | A2, B2, A3 | ; | Sample × Coefficient   |

|      | ADD | .L1  | A4, A3, A4 | ; | Accumulate result      |

### FIRLOOP:

\*A1++, A2 ; Fetch next sample LDH D1 \*B1++, B2 ; Fetch next coefficient LDH .D2 BO. 1. BO : Decrement loop count [B0] SUB .L2 FIRLOOP : Branch if non-zero [BO] B .S2 11 MPY .M1X A2, B2, A3 ; Sample  $\times$  Coefficient ADD .L1 A4. A3. A4 : Accumulate result

### Run in parallel

| Load a halfword (16 bits) |     |      |          |      |                             |

|---------------------------|-----|------|----------|------|-----------------------------|

|                           |     |      |          |      |                             |

| FIRLOOP                   | : ↓ |      |          |      |                             |

|                           | LDH | .D1  | *A1++, A | .2 ; | Fetch next sample           |

|                           | LDH | .D2  | *B1++, B | ;2   | Fetch next coefficient      |

| [BO]                      | SUB | .L2  | BO, 1, B | ;0   | Decrement loop count        |

| [BO]                      | В   | .S2  | FIRLOOP  | ;    | Branch if non-zero          |

|                           | MPY | .M1X | A2, B2,  | A3 ; | Sample $\times$ Coefficient |

|                           | ADD | .L1  | A4, A3,  | A4 ; | Accumulate result           |

|          |     | Do t | his on unit D1 |   |                        |

|----------|-----|------|----------------|---|------------------------|

| FIRLOOP: |     | Ļ    |                |   |                        |

|          | LDH | .D1  | *A1++, A2      | ; | Fetch next sample      |

|          | LDH | .D2  | *B1++, B2      | ; | Fetch next coefficient |

| [BO]     | SUB | .L2  | BO, 1, BO      | ; | Decrement loop count   |

| [BO]     | В   | .S2  | FIRLOOP        | ; | Branch if non-zero     |

|          | MPY | .M1X | A2, B2, A3     | ; | Sample × Coefficient   |

|          | ADD | .L1  | A4, A3, A4     | ; | Accumulate result      |

### FTRLOOP: LDH .D1 \*A1++, A2 ; Fetch next sample LDH .D2 \*B1++, B2 ; Fetch next coefficient BO. 1. BO : Decrement loop count [B0] SUB .L2 FIRLOOP : Branch if non-zero [BO] B .S2 MPY .M1X A2, B2, A3 ; Sample $\times$ Coefficient 11 ADD .L1 A4, A3, A4 ; Accumulate result

Use the cross path

# FIRLOOP: LDH .D1 \*A1++, A2 ; Fetch next sample LDH .D2 \*B1++, B2 ; Fetch next coefficient || [B0] SUB .L2 B0, 1, B0 ; Decrement loop count || [B0] B .S2 FIRLOOP ; Branch if non-zero || MPY .M1X A2, B2, A3 ; Sample × Coefficient || ADD .L1 A4, A3, A4 ; Accumulate result

Predicated instruction (only if B0 non-zero)

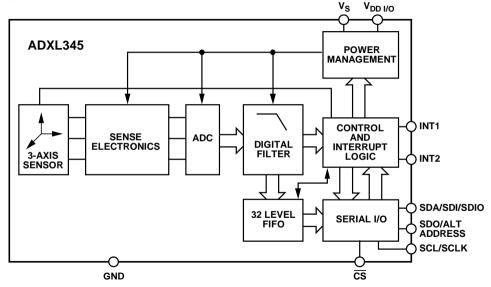

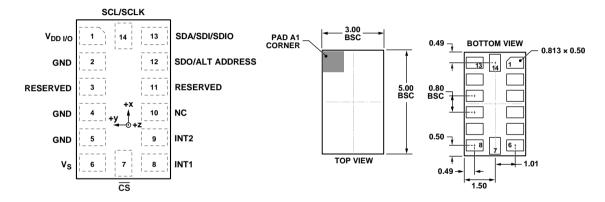

### Analog Devices ADXL345 Accelerometer

### 14 pins, 3mm by 5mm

### DE1-SoC Connections to the ADXL345 Accelerometer

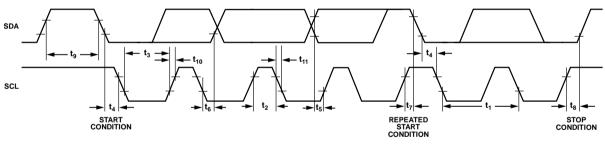

## I<sup>2</sup>C Bus Protocol

# ADXL345 Registers (30, 8-bit)

| Addre        | SS      |                |      |                    |                                                           |

|--------------|---------|----------------|------|--------------------|-----------------------------------------------------------|

| Hex          | Dec     | Name           | Туре | <b>Reset Value</b> | Description                                               |

| 0x00         | 0       | DEVID          | R    | 11100101           | Device ID                                                 |

| 0x01 to 0x1C | 1 to 28 | Reserved       |      |                    | Reserved; do not access                                   |

| 0x1D         | 29      | THRESH_TAP     | R/W  | 0000000            | Tap threshold                                             |

| 0x1E         | 30      | OFSX           | R/W  | 00000000           | X-axis offset                                             |

| 0x1F         | 31      | OFSY           | R/W  | 00000000           | Y-axis offset                                             |

| 0x20         | 32      | OFSZ           | R/W  | 00000000           | Z-axis offset                                             |

| 0x21         | 33      | DUR            | R/W  | 00000000           | Tap duration                                              |

| 0x22         | 34      | Latent         | R/W  | 00000000           | Tap latency                                               |

| 0x23         | 35      | Window         | R/W  | 00000000           | Tap window                                                |

| 0x24         | 36      | THRESH_ACT     | R/W  | 00000000           | Activity threshold                                        |

| 0x25         | 37      | THRESH_INACT   | R/W  | 00000000           | Inactivity threshold                                      |

| 0x26         | 38      | TIME_INACT     | R/W  | 00000000           | Inactivity time                                           |

| 0x27         | 39      | ACT_INACT_CTL  | R/W  | 0000000            | Axis enable control for activity and inactivity detection |

| 0x28         | 40      | THRESH_FF      | R/W  | 0000000            | Free-fall threshold                                       |

| 0x29         | 41      | TIME_FF        | R/W  | 0000000            | Free-fall time                                            |

| 0x2A         | 42      | TAP_AXES       | R/W  | 00000000           | Axis control for single tap/double tap                    |

| 0x2B         | 43      | ACT_TAP_STATUS | R    | 00000000           | Source of single tap/double tap                           |

| 0x2C         | 44      | BW_RATE        | R/W  | 00001010           | Data rate and power mode control                          |

| 0x2D         | 45      | POWER_CTL      | R/W  | 00000000           | Power-saving features control                             |

| 0x2E         | 46      | INT_ENABLE     | R/W  | 00000000           | Interrupt enable control                                  |

| 0x2F         | 47      | INT_MAP        | R/W  | 00000000           | Interrupt mapping control                                 |

| 0x30         | 48      | INT_SOURCE     | R    | 00000010           | Source of interrupts                                      |

| 0x31         | 49      | DATA_FORMAT    | R/W  | 00000000           | Data format control                                       |

| 0x32         | 50      | DATAX0         | R    | 00000000           | X-Axis Data 0                                             |

| 0x33         | 51      | DATAX1         | R    | 00000000           | X-Axis Data 1                                             |

| 0x34         | 52      | DATAY0         | R    | 0000000            | Y-Axis Data 0                                             |

| 0x35         | 53      | DATAY1         | R    | 0000000            | Y-Axis Data 1                                             |

| 0x36         | 54      | DATAZ0         | R    | 0000000            | Z-Axis Data 0                                             |

| 0x37         | 55      | DATAZ1         | R    | 0000000            | Z-Axis Data 1                                             |

| 0x38         | 56      | FIFO_CTL       | R/W  | 0000000            | FIFO control                                              |

| 0x39         | 57      | FIFO_STATUS    | R    | 00000000           | FIFO status                                               |

# Register Documentation (only 3 pages)

#### REGISTER DEEINITIONS

#### Register 0x00—DEVID (Read Only) D7 D6 D5 D4 D3 D2 0

The DEVID register holds a fixed desice ID code of 0xES (345 octal).

### Register (v10 TURESH TAR (Regd(White)

The THRESH TAP register is eight bits and holds the threshold value for tap interrupts. The data format is unsigned, therefore, the magnitude of the tan event is compared with the value in THRESH\_TAP for normal tap detection. The scale factor is 62.5 mail SR (that is (trEE = 16 e). A value of 0 may result in undesirable behavior if single tap/double tap interrupts are enabled

#### Register 0x1E. Register 0x1E. Register 0x20\_OESY. OFSY, OFSZ (Read/Write)

The OFSX. OFSY, and OFSZ registers are each eight bits and offer user-set offset adjustments in twos complement format with a scale factor of 15.6 mail SB (that is dw7E = 2.e). The value stored in the offset registers is automatically added to the acceleration data, and the resulting value is stored in the output data registers. For additional information regarding office calibration and the use of the offset registers, refer to the Offset Calibration section.

#### Register (v 21-DUR (Regd/Write)

The DUR register is eight bits and contains an unsigned time value representing the maximum time that an event must be above the THRESH. TAP threshold to qualify as a tap event. The scale factor is 625 m/I SB A value of 0 disables the simple tan/ double tap functions.

#### Register 0x22-Latent (Read/Write)

The latent register is eight bits and contains an unsigned time value representing the unit time from the detection of a tan event to the start of the time window (defined by the window register) during which a possible second tap event can be detected. The scale factor is 1.25 ms/L5B. A value of 0 disables the double tap

#### Realister 0x22-Window (Read/Weite)

The azimbose maintee is sight hits and contains an unsigned time value representing the amount of time after the expiration of the between times (determined by the latent mainter) during which a second valid tan can beein. The scale factor is 1.25 ms/LSR A value of 0 disables the double tap function.

#### Register 0x24-TURESH ACT (Regd/Maite)

The THRESH ACT register is cight hits and holds the threshold value for detecting activity. The data format is unsigned, so the magnitude of the activity event is compared with the value in the THRESH ACT register. The scale factor is 62.5 me/LSB. A makes of 0 mere enough in condenies bla hadronics if the activity interrupt is enabled.

#### Reakter 0x25\_THRESH\_INACT (Read/Write)

The THRESH\_INACT register is eight bits and holds the threshold value for detecting inactivity. The data format is unsigned so. the magnitude of the inactivity event is compared with the value in the TURESH INACT excision. The code factor is 63.5 and 5R A value of 0 may result in undesirable behavior if the inactivity interrupt is enabled.

#### Register 0x26-TIME INACT (Read/Write)

The TIME INACT register is eight hits and contains an unsigned time value representing the amount of time that acceleration must be less than the value in the THRESH\_INACT register for inactivity to be declared. The scale factor is 1 sec/LSB. Unlike the other interrupt functions which use unfiltened data (see the Threshold section), the inactivity function uses filtered output data. At least one control sample must be reperated for the inactivity interrupt to be triggered. This results in the function appearing unresponsive if the TIME\_INACT register is set to a Register 0x29-TIME FF (Regd/Write) value less than the time constant of the output data rate. A value of 0 results in an interrupt when the output data is less than the value in the THRESH INACT register.

#### Register 0x27—ACT\_INACT\_CTL (Read/Write)

| D7<br>ACT ac/dc | D6<br>ACT_X enable   |                | D4<br>ACT_Z enable | ľ |

|-----------------|----------------------|----------------|--------------------|---|

| D3              | D2<br>INACT_X enable | D1             | D0                 | l |

| P64,130/00      | INPL1_X HIGH         | INPL1_F INADIE | INVIT'S BURNE      | ŋ |

#### ACT AC/DC and INACT AC/DC Bits

A setting of 0 selects dc-coupled operation, and a setting of 1 enables ac-coupled operation. In dc-coupled operation, the current acceleration marnitude is compared directly with THRESH ACT and THRESH INACT to determine whether activity or inactivity is detected.

In ac-coupled operation for activity detection, the acceleration value at the start of activity detection is taken as a reference value. New semples of acceleration are then command to this reference value, and if the marnitude of the difference exceeds the THRESH\_ACT value, the device triggers an activity interrupt.

Similarly in as compled operation for inactivity detection a reference value is used for comparison and is updated whenever Register 0x28-ACT TAP STATUS (Road Only) the denice exceeds the inactivity threshold. After the reference value is selected, the device commares the magnitude of the difference between the reference when and the correct acceleration with THRESH. INACT. If the difference is less than the value in ACT x Source and TAP x Source Bits THRESH\_INACT for the time in TIME\_INACT, the device is considered inactive and the inactivity interrupt is trippered.

#### ACT x Enable Bits and INACT x Enable Bits

A setting of 1 enables x-, y-, or z-axis participation in detectine activity or inactivity. A setting of 0 excludes the selected axis from participation. If all area are excluded, the function is disabled For activity detection, all participating axes are logically ORed. causing the activity function to trigger when any of the participating axes exceeds the threshold. For inactivity detection, all participating axes are logically ANDird, causing the inactivity function to tripper only if all participating axes are below the threshold for the specified time.

#### Register 0x28-THRESH FF (Regd/Write)

The THRESH. FF register is eight hits and holds the threshold value, in unsigned format, for free-fall detection. The acceleration on all axes is compared with the value in THRESH FF to determine if a free-fall exert occurred. The scale factor is 62.5 me/LSB. Note that a value of 0 me may result in undesirable behavior if the freefall interrunt is enabled. Values between 300 mer and 600 mer (0x05 to 0x09) are recommended.

The TIME FF register is gight bits and stores an unsigned time value representing the minimum time that the value of all axes must be less than THRESH FF to generate a free-fall interrupt. The scale factor is 5 ms/I SB. A value of 0 may read; in undesirable behavior if the free-fall interrupt is enabled. Values between 100 ms and 350 ms (0x14 to 0x46) are recommended

| Zenable | Regis | Register 0x2A—TAP_AXES (Read/Write) |    |    |          |                 |                 |                 |  |  |  |

|---------|-------|-------------------------------------|----|----|----------|-----------------|-----------------|-----------------|--|--|--|

|         | D7    | D6                                  | DS | D4 |          |                 |                 | D0              |  |  |  |

|         | 0     | 0                                   | 0  | 0  | Suppress | TAP_X<br>enable | TAP_Y<br>enable | TAP_Z<br>enable |  |  |  |

#### Suppress Bit

Setting the suppress bit suppresses double tap detection if acceleration arouter than the value in TURESH. TAP is present between tars. See the Tan Detection section for more details.

#### TAP x Enable Bits

A setting of Lin the TAP, X mahls, TAP, X mahle, or TAP, Z enable bit enables x., y., or z-axis participation in tan detection. A settine of 0 excludes the selected axis from participation in

| D7 |                 |                 |                 |        |                 |                 | DB              |

|----|-----------------|-----------------|-----------------|--------|-----------------|-----------------|-----------------|

| 0  | ACT_X<br>source | ACT_Y<br>source | ACT_Z<br>source | Asleep | TAP_X<br>source | TAP_Y<br>SOURCE | TAP_Z<br>source |

These bits indicate the first axis involved in a tap or activity event. A setting of 1 corresponds to involvement in the event, and a setting of 0 corresponds to no involvement. When new data is available, these bits are not cleared but are overwritten by the new data. The ACT\_TAP\_STATUS register should be read before clearing the interrupt. Disabling an axis from participation clears the corresponding source bit when the pest activity or single tap/double tap event occurs.

#### Asleep Bit

A setting of 1 in the asleen hit indicates that the part is asleen and a setting of 0 indicates that the part is not asleep. This bit togales only if the desice is configured for auto sleep. See the AUTO SLEEP Bit section for more information on autosleep mode

#### Register 0x2C-BW\_RATE (Regd/Write) D7 D6 D5 D4 D3 D2 D1 D0

#### 0 0 0 LOW\_POWER LOW POWER Bit

A setting of 0 in the LOW\_POWER bit selects normal operation and a setting of 1 selects reduced power operation, which has someshot higher noise (see the Power Modes section for details) Rate Bits

These bits select the device bandwidth and output data rate (see Table 7 and Table 8 for details). The default value is 0x0.4, which translates to a 100 Hz output data rate. An output data rate should he selected that is appropriate for the communication protocol and frequency selected. Selecting too high of an output data rate with a low communication speed results in samples being discarded.

#### Register 0x2D-POWER\_CTL (Read/Write) D7 D6 D5 D4 D3 D2 D1 D6

#### 0 0 Link AUTO\_SLEEP Measure Sleep Wakeup Link Bit

A setting of 1 in the link hit with both the activity and inactivity functions enabled delays the start of the activity function until inactivity is detected. After activity is detected, inactivity detection begins, preventing the detection of activity. This bit serially links the activity and inactivity functions. When this bit is set to 0. the inactivity and activity functions are concurrent. Additional information can be found in the Link Mode section

When clearing the link bit, it is recommended that the part be placed into standly mode and then set back to measurement mode with a subsequent write. This is done to ensure that the device is properly biased if sleep mode is manually disabled: otherwise, the first few samples of data after the link bit is cleared may have additional noise, especially if the device was asleep when the bit was cleared.

#### AUTO SLEEP BR

Other link hit is not a patting of 1 in the AUTO's SUEEP hit meldes the auto-sleep functionality. In this mode, the ADXL345 automatically switches to sleep mode if the inactivity function is enabled and inactivity is detected (that is, when acceleration is below the THRESH INACT value for at least the time indicated he TIME INACT). If activity is also analyzed the ADVI 345. automatically wakes up from deep after detecting activity and returns to operation at the output data rate set in the BW\_RATE register. A setting of 0 in the AUTO, SLEEP bit disables automatic switching to sleep mode. See the description of the Sleep Bit in this section for more information on sleep mode.

If the link bit is not set, the AUTO\_SLEEP feature is disabled and setting the AUTO\_SUFEP bit does not have an impact on device operation. Refer to the Link Bit section or the Link Mode section for more information on utilization of the link feature.

When clearing the AUTO: SI FEP bit, it is recommended that the part be placed into standby mode and then set back to measurement mode with a subsequent write. This is done to ensure that the device is properly biased if sleep mode is manually disabled: otherwise, the first frae samples of data after the AUTO, SLEEP, bit is cleared may have additional noise, especially if the device yess asleen when the hit year cleared

#### Measure Bit

A setting of 0 in the measure bit places the part into standby mode, and a setting of 1 places the part into measurement mode. The ADXL345 powers up in standby mode with minimum power consumption.

### Share Bit

A setting of 0 in the sleep bit puts the part into the normal mode of operation, and a setting of 1 places the part into sleep mode. Sleep mode suppresses DATA\_READY, stops transmission of data to FIFO, and switches the sampling rate to one specified by the wakeup bits. In sleep mode, only the activity function can be used. When the DATA\_READY interrunt is suppressed, the output data registers (Register 0x32 to Register 0x37) are still undated at the sampling rate set by the wakeup bits (D1:D0).

When clearing the shoes hit, it is recommended that the part he placed into standby mode and then set back to measurement mode with a subsequent write. This is done to ensure that the device is properly biased if sleep mode is manually disabled. otheracise, the first first samples of data after the sleep hit is cleared may have additional noise, carecially if the device was schem when the hit year cleaned

#### Weberry Bits

These bits control the frequency of readings in sleep mode as described in Table 20.

| able 2 | 0. Frequency of | Readings in Sleep Mode |

|--------|-----------------|------------------------|

|        | Setting         |                        |

|        |                 |                        |

| D1 | DO | Frequency (Hz) |

|----|----|----------------|

| 0  | 0  | 8              |

| 0  | 1  | 4              |

| 1  | 0  | 2              |

| 1  | 1  | 1              |

#### Register 0x2E—INT\_ENABLE (Read/Write)

| D7         |           | DS         | D4       |

|------------|-----------|------------|----------|

| DATA_READY |           | DOUBLE_TAP | Activity |

| D3         | D2        | D1         | D0       |

| Inactivity | FREE_FALL | Watermark  | Overrun  |

Setting bits in this register to a value of 1 enables their respective functions to generate interrupts, whereas a value of 0 prevents the functions from generating interrupts. The DATA\_READY watermark, and overrun bits enable only the interrupt output the functions are shows enabled. It is recommended that internents be configured before enabling their outputs.

#### Register 0x2F-INT MAP (R/W)

| D7<br>DATA_READY | D6<br>SINGLE_TAP | DS<br>DOUBLE_TAP | D4<br>Activity |

|------------------|------------------|------------------|----------------|

| D3               | D2<br>FREE FALL  | D1<br>Watermark  | D0             |

| Inactivity       | FREE_FALL        | Watermark        | Overrun        |

Any bits set to 0 in this register send their respective interrupts to the INT1 pin, whereas bits set to 1 send their respective interrupts to the INT2 pin. All selected interrupts for a sizen pin are Offed.

#### Resister 0x20 INT SOURCE (Read Oak)

| D7<br>DATA_READY | D6         | DS         | D4       |

|------------------|------------|------------|----------|

| DATA_READY       | SINGLE_TAP | DOUBLE_TAP | Activity |

| D3<br>Inactivity | D2         | D1         | D0       |

| Inactivity       | FREE_FALL  | Watermark  | Overrun  |

Bits set to 1 in this register indicate that their respective functions have triggered an event, whereas a value of 0 indicates that the corresponding count has not occurred. The DATA\_READY watermark, and overrun bits are always set if the corresponding events occur, regardless of the INT\_ENABLE register settings, and are cleared by reading data from the DATAX, DATAY, and DATAZ registers. The DATA\_READY and watermark bits may require multiple reads, as indicated in the FIFO mode descriptions in the UEO section. Other hits and the common ding interments are cleared by reading the INT\_SOURCE register.

### Register 0x31-DATA FORMAT (Read/Write) D6 D5 D4 D3 D2

The DATA FORMAT register controls the presentation of data to Resistor (hr?? through Resistor (hr?? All data excent that for the ±16 e range, must be clipped to moid rollower.

#### SELF TEST Bit

A setting of 1 in the SELF. TEST bit applies a self-test force to the sensor, causing a shift in the output data. A value of 0 disables

#### CDI Die

A value of 1 in the SPI bit sets the device to 3 seize SPI mode. and a value of 0 sets the device to 4-wire SPI mode

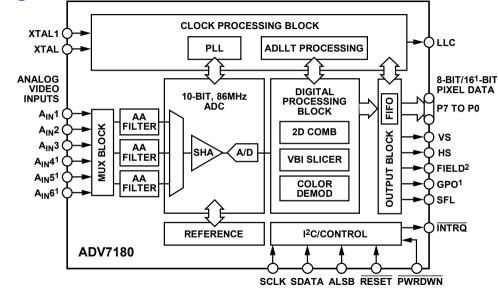

Analog Devices ADV7180 Video Decoder

| Add | ress     |                                                    | r       | 1            |                | r            | 1                      | 1               |                      | 1                   |                  | Reset     | 1     |

|-----|----------|----------------------------------------------------|---------|--------------|----------------|--------------|------------------------|-----------------|----------------------|---------------------|------------------|-----------|-------|

| Dec | Hex      | Register Name                                      | ĸw      | 7            | 6              | 5            | 4                      | 3               | 2                    | 1                   | •                | Value     | (Hex) |

| 0   | 00       | Input Control                                      | ίκων    | VID_SEL[3]   | VID_SEL[2]     | VID_SEL[1]   | VID_SEL[0]             | INSEL[3]        | INSEL[2]             | INSEL[1]            | INSEL[0]         | 00000000  | 00    |

| 1   | 01       | Video Selection                                    | 8W      |              | ENHSPLL        | BETACAM      |                        | ENVSPROC        | SOPE                 |                     |                  | 11001000  | CB    |

| 3   | 03       | Output Control                                     | 8W      | VBI_EN       | 100            | OF_SEL[3]    | OF_SEL[2]              | OF_SEL[1]       | OF_SEL[0]            |                     | SD_DUP_AV        | 00001100  | 0C    |

| 4   | 04       | Extended Output Control                            | 8W      | 8T.656-4     |                |              |                        | TIM_OE          | BL_C_VBI             | EN_SFL_PIN          | Range            | 01xx0101  | 45    |

| 5   | 05       | Reserved                                           |         |              |                |              |                        |                 |                      |                     |                  |           |       |

| 6   | 06       | Reserved                                           |         |              |                |              |                        |                 |                      |                     |                  |           |       |

| 7   | 07       | Autodetect Enable                                  | 8W      | AD_SEC525_EN | AD_SECAM_EN    | AD_N443_EN   | AD_P60_EN              | AD_PALN_EN      | AD_PALM_EN           | AD_NTSC_EN          | AD_PAL_EN        | 01111111  | ΤF    |

| 8   | 08       | Contrast                                           | 8W      | CON[7]       | CON[6]         | CON(5)       | CON[4]                 | CON[3]          | CON[2]               | CON[1]              | CON[0]           | 10000000  | 80    |

| 9   | 09       | Reserved                                           |         |              |                |              |                        |                 |                      |                     |                  |           |       |

| 10  | 0A       | Brightness                                         | 8W      | BR1[7]       | £191(d)        | BRI[5]       | 880[4]                 | BRI[3]          | BRI[2]               | £R(1)               | 860[0]           | 00000000  | 00    |

| 11  | 0B       | Hae                                                | έw.     | HUE[7]       | HUE[6]         | HUE(S)       | HUE[4]                 | HUE[3]          | HUE[2]               | HUE[1]              | HUE[0]           | 00000000  | 00    |

| 12  | 0C       | Default Value Y                                    | 8W      | DEF_Y[5]     | DEF_Y[4]       | DEF_Y[3]     | DEF_Y[2]               | DEF_Y[1]        | DEF_Y[0]             | DEF_VAL_<br>AUTO_EN | DEF_VAL_EN       | 00110110  | 36    |

| 13  | 0D       | Default Value C                                    | ŔW      | DEF_C[7]     | DEF_C[6]       | DEF_C[5]     | DEF_C[4]               | DEF_C[3]        | DEF_C[2]             | DEF_C[1]            | DEF_C[0]         | 01111100  | π     |

| 14  | 0E       | ADI Control 1                                      | ŔW      |              |                | SUB_USR_EN   |                        |                 |                      |                     |                  | 00000000  | 00    |

| 15  | OF       | Power Management                                   | ŔW      | RESET        |                | PWRDWN       |                        |                 | PD8P                 |                     |                  | 00000000  | 00    |

| 16  | 10       | Status 1                                           | ĸ       | COL_KILL     | AD_RESULT[2]   | AD_RESULT[1] | AD_RESULT[0]           | FOLLOW_PW       | FSC_LOCK             | LOST_LOCK           | IN_LOCK          | -         | -     |

| 17  | 11       | IDENT                                              | Ŕ       | IDENT[7]     | IDENT(6)       | IDENT[5]     | IDENT[4]               | IDENT[3]        | IDENT[2]             | IDENT[1]            | IDENT[0]         | 00011100  | 1C    |

| 18  | 12       | Status 2                                           | Ŕ       |              |                | FSC NSTD     | LL NSTD                | MV AGC DET      | MV PS DET            | MVCST3              | MVCS DET         | -         | -     |

| 19  | 13       | Status 3                                           | Ŕ.      | PAL_SW_LOCK  | INTERLACED     | STD FLD LEN  | FREE_FUN_ACT           | Reserved        | SD_OP_SOHz           | GEND                | INST_HLOCK       | +         | -     |

| 20  | 14       | Analog Clamp Control                               | ŔW      |              |                |              | CCLEN                  |                 |                      |                     |                  | 00010010  | 12    |

| 21  | 15       | Digital Clamp Control 1                            | ŔW      |              | OCT[1]         | DCT[0]       | DCFE                   |                 |                      |                     |                  | 0000xxx   | 00    |

| 22  | 16       | Reserved                                           | Г       |              |                |              |                        |                 |                      |                     |                  |           | 1     |

| 23  | 17       | Shaping Filter Control 1                           | ŔW      | CSFM[2]      | CSFM[1]        | CSFM[0]      | YSFM(4)                | YSFM(3)         | YSFM[2]              | YSFM[1]             | YSEM(0)          | 00000001  | 01    |

| 24  | 18       | Shaping Filter Control 2                           | ŔW      | WISEMOVR     |                |              | WYSEM[4]               | WYSFM[3]        | WYSFM[2]             | WYSFM(1)            | WYSENEO          | 10010011  | 93    |

| 25  | 19       | Comb Filter Control                                | ŔW      |              |                |              |                        | NSFSEL[1]       | NSFSEL(0)            | PSFSEL[1]           | PSFSEL[0]        | 11110001  | Ē1    |

| 29  | 1D       | ADI Control 2                                      | ŔW      | TRI_LLC      | EN2EXTAL       |              |                        |                 |                      |                     |                  | 01000xxx  | 40    |

| 39  | 27       | Pixel Delay Control                                | 8W      | SWPC         | AUTO_PDC_EN    | CTA[2]       | CTA[1]                 | CTA(0)          |                      | LTA[1]              | LTA(0)           | 01011000  | 58    |

| 43  | 28       | Misc Gain Control                                  | ŔW      |              | CKE            |              |                        |                 |                      |                     | PW_UPD           | 11100001  | Ē1    |

| 44  | 2C       | AGC Mode Control                                   | ŔW      |              | LAGC[2]        | LAGC[1]      | LAGC[0]                |                 |                      | CAGC[1]             | CAGC[0]          | 10101110  | AE    |

| 45  | 2D       | Chroma Gain Control 1                              | w       | CAGT[1]      | CAGT[0]        |              |                        | CMG[11]         | CMG[10]              | CMG(9)              | CMG(8)           | 11110100  | F4    |

| 45  | 2D       | Chroma Gain 1                                      | Ŕ.      |              |                |              |                        | CG[11]          | CG[10]               | CG(9)               | CGIN             | -         |       |

| 46  | 2E       | Chroma Gain Control 2                              | w       | CMG[7]       | CMG(6)         | CMG[5]       | CMS[4]                 | CMG[3]          | CMG[2]               | CMG(1)              | CMG(0)           | 00000000  | 00    |

| 46  | 2E       | Chroma Gain 2                                      | R       | CG[7]        | CG(6)          | CG[5]        | CG[4]                  | CG[3]           | CG[2]                | CG(1)               | CGER             | -         |       |

| 47  | 2F       | Luma Gain Control 1                                | w       | LAGT[1]      | LAGT(0)        |              |                        | LMG[11]         | LMG[10]              | LMG[9]              | LMG08            | 11113000X | FO    |

| 47  | 2F       | Luma Gain 1                                        | Ŕ.      |              |                |              |                        | LG[11]          | LG[10]               | LG[9]               | LG(8)            |           | -     |

| 48  | 30       | Luma Gain Control 2                                | w       | LMG[7]       | LMG(6)         | LMGEST       | LMG(4)                 | LMG[3]          | LMG[2]               | LMG[1]              | LMG(0)           | 100003001 | 00    |

| 48  | 30       | Luma Gain 2                                        | Ŕ.      | LGE71        | LG(6)          | LGES         | LGE4                   | LG[3]           | LG[2]                | LG[1]               | LG(0)            |           |       |

| 49  | 31       | VS/Field Control 1                                 | 8W      |              |                |              | NEWAVMODE              | HVSTIM          |                      |                     |                  | 00010010  | 12    |

| 50  | 32       | VS/Field Control 2                                 | 8W      | VSEHO        | VSBHE          |              |                        |                 |                      |                     |                  | 01000001  | 41    |

| 51  | 33       | VS/Field Control 3                                 | 8W      | VSEHO        | VSEHE          |              |                        |                 |                      |                     |                  | 10000100  | 84    |

| 52  | 34       | HS Position Control 1                              | 8W      |              | HSB(10)        | H58(9)       | HSB[8]                 |                 | HSE(10)              | HSE[9]              | HSE(8)           | 00000000  | 00    |

| 53  | 35       | HS Position Control 2                              | 8W      | H58[7]       | HSB(6)         | H58[5]       | H5854]                 | H\$8(3)         | H58[2]               | H58(1)              | HSBID            | 00000010  | 02    |

| 54  | 36       | HS Position Control 3                              | 8W      | HSE[7]       | HSEIdi         | HSE(5)       | HSE[4]                 | HSEIN           | HSE[2]               | HSE[1]              | HSEI01           | 00000000  | 00    |

| 55  | 37       | Polarity                                           | RW      | PHS          |                | PV5          |                        | PF              |                      |                     | PCLK             | 00000001  | 01    |

| 56  | 38       | NTSC Comb Control                                  | RW      | CTAPSN[1]    | CTAP5N[0]      | CCMN[2]      | CCMN[1]                | CCMN(0)         | YCMN(2)              | YCMN[1]             | YCMN(0)          | 10000000  | 80    |

| 57  | 39       | PAL Comb Control                                   | RW      | CTAPSP(1)    | CTAPSP[0]      | CCMP[2]      | CCMP[1]                | CCMP(0)         | YCMP[2]              | YCMP[1]             | YCMP(0)          | 11000000  | CO    |

| 58  | 3A       | ADC Control                                        | RW      |              |                |              |                        | PWRDWN_MUX_0    | PWRDWN_MUX_1         | PWRDWN_MUX_2        | MUX PDN override | 00010000  | 10    |

| 61  | 3D       | Manual Window Control                              | RW      |              | CKILLTHR[2]    | CKILLTHR[1]  | COLLTHR[0]             |                 |                      |                     |                  | 01110010  | 82    |

| 65  | 41       | Resample Control                                   | 8W      |              | SFL_IN/        |              |                        | 1               |                      |                     |                  | 00000001  | 01    |

| 72  | 48       | Gernstar Control 1                                 | 8W      | GDECEL[15]   | GDECEL[14]     | GDECEL[13]   | GDECEL[12]             | GDECEL[11]      | GDECEL[10]           | GDECEL(9)           | GDECEL[8]        | 000000000 | 00    |

| 73  | 49       | Gernstar Control 2                                 | 8W      | GDECEL[7]    | GDECEL(6)      | GDECEL[5]    | GDECEL[4]              | GDECEL[3]       | GDECEL[2]            | GDECEL[1]           | GDECEL[0]        | 00000000  | 00    |

| 74  | 4A       | Gernstar Control 3                                 | kw      | GDECOL[15]   | GDECOL[14]     | GDECOL[13]   | GDECOL[12]             | GDECOL[11]      | GDECOL[10]           | GDECOL[9]           | GDECOL(8)        | 00000000  | 00    |

| 75  | 48       | Gernstar Control 4                                 | 8W      | GDECOL[7]    | GDECOL[6]      | GDECOL[5]    | GDECOL[4]              | GDECOL[3]       | GDECOL[2]            | GDECOL[1]           | GDECOL(0)        | 00000000  | 00    |

| 76  | 4C       | Gernstar Control 5                                 | 8W      |              |                |              |                        | GDE_SEL_OLD_ADF |                      |                     | GDECAD           | 100000000 | 00    |

| 77  | 4D       | CTI DNR Control 1                                  | 8W      |              |                | DNR_EN       |                        | CTL_AB[1]       | CTI_AB[0]            | CTL_AB_EN           | CTI_EN           | 11101111  | EF    |

| 78  | 4E       | CTIDNR Control 2                                   | 8W      | CTL_C_TH[7]  | CTI_C_TH[6]    | CTI_C_TH[5]  | CTI_C_TH(4)            | CTI_C_TH[3]     | CTI_C_TH[2]          | CTI_C_TH[1]         | CTI_C_TH(0)      | 00001000  | 08    |

| 80  | 50       | CTIDNR Control 4                                   | 8W      | DNR_TH[7]    | DNR_TH[6]      | DNR_TH[5]    | DNR THE                | DNR_TH[3]       | DNR_TH[2]            | DNR_TH[1]           | DNR_TH(0)        | 00001000  | 08    |

| 81  | 51       | Lock Count                                         | 8W      | FSCLE        | SRLS           | COL[2]       | COL[1]                 | COL[0]          | CILI2                | CIL[1]              | CILIO            | 00100100  | 24    |

| 88  | 58       | VS/FIELD Pin Control                               | RW      |              |                |              |                        |                 | ADC sampling control |                     | VS/FIELD         | 00000000  | 00    |

| 82  | 52       | General-Purpose Outputs <sup>2</sup>               | 8W      |              |                |              | GPO_Enable             | GPO[3]          | GPO[2]               | GPO[1]              | GPO(0)           | 00000000  | 00    |

| 143 | 59<br>8F | General-Purpose Outputs*<br>Free-Run Line Length 1 | WW<br>W |              | LLC_PAD_SEL[2] | LLC_PAD_     | GPO_bnable<br>LLC_PAD_ | arajaj          | GPO[2]               | uno[1]              | anojoj           | 000000000 | 00    |

|     | 1. C     | r new man und Length 1                             | Ľ.      |              |                | SEL[1]       | SELIO                  | 1               |                      | 1                   |                  |           | ~     |

|     |          |                                                    |         |              |                |              |                        |                 |                      |                     |                  |           |       |

| 153 | 99       | CCAP 1                                             | R.      | CCAP1[7]     | CCAP1[6]       | CCAP1[5]     | CCAP1[4]               | CCAP1[3]        | CCAP1[2]             | CCAP1[1]            | CCAP1[0]         | -         | -     |

| Addres         | 15 |                     |      |                     |                     |                     |                     |                      |                      |                        |                        | Reset            |     |

|----------------|----|---------------------|------|---------------------|---------------------|---------------------|---------------------|----------------------|----------------------|------------------------|------------------------|------------------|-----|

| Dec He         | ex | Register Name       | RW   | 7                   | 6                   | 5                   | 4                   | 3                    | 2                    | 1                      | 0                      | Value            | Hex |

| 155 96         | ŝ  | Letterbax 1         | Ŕ    | LB_LCT[7]           | LB_LCT[6]           | LB_LCT[5]           | LB_LCT[4]           | LB_LCT[3]            | LB_LCT[2]            | LB_LCT[1]              | LB_LCT[0]              | -                | -   |

| 156 90         | -  | Letterbax 2         | Ŕ    | LB_LCM[7]           | LB_LCM[6]           | LB_LCM[5]           | LB_LCM[4]           | LB_LCM[3]            | LB_LCM[2]            | LB_LCN[1]              | LB_LCM[0]              | -                | -   |

| 157 90         | >  | Letterbax 3         | Ŕ    | LB_LCB[7]           | LB_LCB[6]           | LB_LCB[5]           | LB_LCB[4]           | LB_LCB[3]            | LB_LCB[2]            | LB_LCB[1]              | LB_LCB(0)              | -                | -   |

| 178 83         | 2  | CNC Enable          | W    |                     |                     |                     |                     |                      | CRC_ENABLE           |                        |                        | 00011100         | 1C  |

| 195 C3         | ŝ  | ADC Switch 1        | RW   | Reserved            | ML0(1[2]            | MUX1[1]             | MUDC1 [0]           | Reserved             | MUX0[2]              | MLIX0[1]               | MILOCO[0]              | 1000030000       | 00  |

| 196 C4         | ι. | ADC Switch 2        | RW   | MAN_MUX_EN          |                     |                     |                     | Reserved             | MUX2[2]              | MLDQ[1]                | MU0C2[0]               | <b>Genoceter</b> | 00  |

| 220 DI         | C  | Letterbax Control 1 | RW   |                     |                     |                     | LB_TH[4]            | LB_TH[3]             | L8_TH[2]             | L8_TH[1]               | LB_TH[0]               | 10101100         | AC  |

| 221 DI         | D  | Letterbax Control 2 | ŔŴ   | LB_SL[3]            | LB_SL[2]            | LB_SL[1]            | LB_SL[0]            | LB_EL[3]             | LB_EL[2]             | LB_EL[1]               | LB_EL(0)               | 01001100         | 4C  |

| 222 Di         | Ē  | ST Noise Readback 1 | Ŕ    |                     |                     |                     |                     | ST_NOISE_VLD         | ST_NOISE[10]         | ST_NOISE[9]            | ST_NOISE[8]            | -                | -   |

| 223 DI         | F  | ST Noise Readback 2 | Ŕ    | ST_NOISE[7]         | ST_NOISE(6)         | ST_NOISE[5]         | ST_NOISE[4]         | ST_NOISE[3]          | ST_NCISE[2]          | ST_NOISE[1]            | ST_NOISE(0)            | -                | -   |

| 224 E0         | 5  | Reserved            |      |                     |                     |                     |                     |                      |                      |                        |                        |                  |     |

| 225 E1         | 1  | SD Offset Cb        | RW   | SD_OFF_CB[7]        | SD_OFF_C8(6)        | SD_OFF_CB[5]        | SD_OFF_CB[4]        | SD_OFF_CB[3]         | SD_OFF_CB[2]         | SD_OFF_C8[1]           | SD_OFF_CB[0]           | 10000000         | 80  |

| 226 E2         | 2  | SD Offset Cr        | RW   | SD_OFF_CR[7]        | SD_OFF_CR(6)        | SD_OFF_CR[5]        | SD_OFF_CR[4]        | SD_OFF_CR(3)         | SD_OFF_CR[2]         | SD_OFF_CR[1]           | SD_OFF_CR[0]           | 10000000         | 80  |

| 227 E3         | 5  | SD Saturation Cb    |      | SD_SAT_CB[7]        | SD_SAT_CB[6]        | SD_SAT_CB[5]        | SD_SAT_CB[4]        | SD_SAT_CB[3]         | SD_SAT_C8[2]         | SD_SAT_CB[1]           | SD_SAT_CB(0)           | 10000000         | 80  |

| 228 E4         | 5  | SD Saturation Cr    | 8W   | SD_SAT_CR[7]        | SD_SAT_CR(6)        | SD_SAT_CR[5]        | SD_SAT_CR(4)        | SD_SAT_CR[3]         | SD_SAT_CR[2]         | SD_SAT_CR[1]           | SD_SAT_CR(0)           | 10000000         | 80  |

| 229 ES         | 5  | NTSC V Bit Begin    | itw. | NVBEGDELO           | NVBEGDELE           | NVBEGSIGN           | NVBEG[4]            | NVBEG[3]             | NVBEG[2]             | NVBEG(1)               | NVBEG(0)               | 00100101         | 25  |

| 230 É6         | 5  | NTSC V Bit End      | itw  | NVENDDELO           | NVENDDELE           | NVENDSIGN           | NVEND[4]            | NVEND[3]             | NVEND[2]             | NVEND(1)               | NVEND[0]               | 00000100         | 04  |

| 231 E7         | r  | NTSC F Bit Toggle   | RW   | NFTOGDELO           | NFTOGDELE           | NFTOGSIGN           | NFTOG[4]            | NFTOG[3]             | NFTOG[2]             | NFTOG[1]               | NFTOG(0)               | 01100011         | 63  |

| 232 E8         | 5  | PAL V Bit Begin     | RW   | PVBEGDELO           | PVBEGDELE           | PVBEGSIGN           | PVEEC(4)            | PV8EG[3]             | PV8EG[2]             | PVBEG[1]               | PVBEG(0)               | 01100101         | 65  |

| 233 ÉS         | 2  | PAL V Bit End       | 8W   | PVENDDELO           | PVENDOELE           | PVENDSIGN           | PVEND(4)            | PVEND[3]             | PVEND[2]             | PVEND[1]               | PVEND(0)               | 00010100         | 14  |

| 234 E <i>F</i> | 1  | PAL F Bit Toggle    | 8W   | PFTOGDELO           | PFTOGDELE           | PFTOGSIGN           | PFTOG[4]            | PFTOG(3)             | PFTOG[2]             | PFTOG[1]               | PFTOG[0]               | 01100011         | 63  |

| 235 E8         | 5  | Volank Control 1    | itW. | NVBIOLCM[1]         | NVBIOLON(0)         | NVBIELCM[1]         | NVBELCM[0]          | PVBIOLCM[1]          | PVBIOLCM[0]          | PVBELCM[1]             | PVBIELCM(0)            | 01010101         | 55  |

| 236 ÉC         |    | Volank Control 2    | itw  | NVBIOCCM[1]         | NVBIOCCM[0]         | NVBIECCN[1]         | NVBECCM(0)          | PVBIOCCM[1]          | PVBIOCCM[0]          | PVBIECCM[1]            | PVBIECCM[0]            | 01010101         | 55  |

| 143 F3         | 1  | AFE_CONTROL 1       | itw  |                     |                     |                     |                     | AA_FILT<br>MAN_OVR   | AA_FILT_EN[2]        | AA_FILT_EN[1]          | AA_FET_EN(0)           | 00000000         | 00  |

| 244 F4         | •  | Drive Strength      | RW   |                     |                     | DR_STR[1]           | DR_STR0(            | DR_STR_C[1]          | DR_STR_C(0)          | DR_STR_S[1]            | DR_STR_S(0)            | xx010101         | 15  |

| 48 F8          | 1  | IF Comp Control     | RW   |                     |                     |                     |                     |                      | FFILTSEL[2]          | IFFILTSEL[1]           | IFFETSEL[0]            | 00000000         | 00  |

| 49 FS          | 2  | VS Mode Control     | RW   |                     |                     |                     |                     | VS_COAST_<br>MODE[1] | VS_COAST_<br>MODE(0) | EXTEND_VS_<br>MIN_FREQ | EXTEND_VS_<br>MAX_FREQ | 00000011         | 03  |

| 51 FB          | 1  | Peaking Control     | RW   | PEANING_<br>GAIN[7] | PEAKING_<br>GAIN[6] | PEANING_<br>GAIN(5) | PEAKING_<br>GAIN(4) | PEAKING_<br>GAIN[3]  | PEAKING_<br>GAIN[2]  | PEAKING_<br>GAIN(1)    | PEAKING_<br>GAIN(0)    | 01000000         | 40  |

| 152 FC         | 1  | Coring Threshold    | itw  | DNR_TH2[7]          | DNR_TH2(6)          | DNR_TH2[5]          | DNR_TH2[4]          | DNR_TH2[3]           | ONR TH2[2]           | DNR TH2[1]             | DNR_TH2(0)             | 00000100         | 04  |

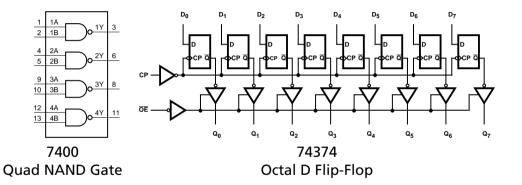

### Fixed-function: The 7400 series

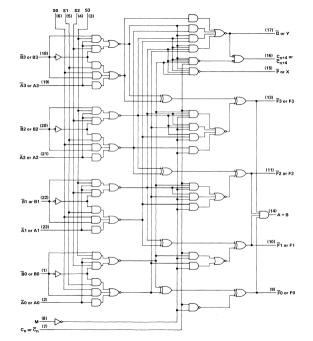

The 74181 4-bit ALU

The 74181 4-bit ALU