# Efficient, Deterministic and Deadlock-free Concurrency

### Nalini Vasudevan

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

**COLUMBIA UNIVERSITY**

### **ABSTRACT**

# **Efficient, Deterministic and Deadlock-free Concurrency**

#### Nalini Vasudevan

Concurrent programming languages are growing in importance with the advent of multicore systems. Two major concerns in any concurrent program are data races and deadlocks. Each are potentially subtle bugs that can be caused by non-deterministic scheduling choices in most concurrent formalisms. Unfortunately, traditional race and deadlock detection techniques fail on both large programs, and small programs with complex behaviors.

We believe the solution is model-based design, where the programmer is presented with a constrained higher-level language that prevents certain unwanted behavior. We present the SHIM model that guarantees the absence of data races by eschewing shared memory.

This dissertation provides SHIM based techniques that aid determinism - models that guarantee determinism, compilers that generate deterministic code and libraries that provide deterministic constructs. Additionally, we avoid deadlocks, a consequence of improper synchronization. A SHIM program may deadlock if it violates a communication protocol. We provide efficient techniques for detecting and deterministically breaking deadlocks in programs that use the SHIM model.

We evaluate the efficiency of our techniques with a set of benchmarks. We have also extended our ideas to other languages. The ultimate goal is to provide deterministic deadlock-free concurrency along with efficiency. Our hope is that these ideas will be used in the future while designing complex concurrent systems.

# **Table of Contents**

| I  | Intr | roduction                                      | 1  |

|----|------|------------------------------------------------|----|

| 1  | The  | Problem                                        | 2  |

|    | 1.1  | Terminology                                    | 4  |

|    | 1.2  | Problem Statement                              | 5  |

|    | 1.3  | Design Considerations                          | 5  |

|    |      | 1.3.1 Performance                              | 5  |

|    |      | 1.3.2 Scalability                              | 6  |

|    |      | 1.3.3 Programmer Flexibility and Ease of Use   | 6  |

|    | 1.4  | Thesis Outline                                 | 6  |

| 2  | Bacl | kground                                        | 8  |

|    | 2.1  | Problems with concurrent programming           | 8  |

|    | 2.2  | Concurrent programming models                  | 9  |

|    | 2.3  | Determinizing tools                            | 13 |

|    | 2.4  | Model checkers and verifiers                   | 14 |

|    |      |                                                |    |

| II | De   | terminism                                      | 16 |

| 3  | The  | SHIM Model                                     | 18 |

| 4  | SHI  | M on a Shared Memory Architecture              | 26 |

|    | 4.1  | Reviewing SHIM                                 | 27 |

|    | 4.2  | Design exploration with SHIM                   | 29 |

|    |      | 4.2.1 Porting and parallelizing a JPEG decoder | 29 |

|    |      | 4.2.2 Parallelizing an FFT                     | 32 |

|    |      | 4.2.3 Race freedom                             | 32 |

|    | 4.3  | Generating Pthreads code for SHIM              | 32 |

|    |      | 4.3.1 Mutexes and condition variables          | 33 |

|    |      | 4.3.2 The static approach                      | 33 |

|    |      | 4.3.3 Implementing rendezvous communication    | 34 |

|   |     | 4.3.4    | Starting and terminating tasks | . 36 |

|---|-----|----------|--------------------------------|------|

|   |     | 4.3.5    | Optimizations                  | . 38 |

|   | 4.4 | Experi   | imental results                | . 38 |

|   | 4.5 | Related  | d work                         | . 39 |

|   | 4.6 |          | usions                         |      |

| 5 | SHI | M on a   | Heterogeneous Architecture     | 41   |

|   | 5.1 | The Ce   | ell Processor                  | . 42 |

|   |     | 5.1.1    | DMA and Alignment              | . 42 |

|   |     | 5.1.2    | Mailboxes and Synchronization  |      |

|   | 5.2 | Our Co   | ompiler                        | . 43 |

|   |     | 5.2.1    | Code for the PPE               | . 44 |

|   |     | 5.2.2    | Code for the SPEs              | . 44 |

|   | 5.3 | Collect  | ting Performance Data          | . 48 |

|   | 5.4 | Experi   | imental Results                | . 50 |

|   | 5.5 | Related  | d Work                         | . 52 |

|   | 5.6 | Conclu   | usions                         | . 53 |

| 6 | SHI | M as a l | Library                        | 55   |

|   | 6.1 | SHIM     | as a Library Versus a Language | . 55 |

|   | 6.2 |          | d Work                         |      |

|   | 6.3 |          | rrency in Haskell              |      |

|   | 6.4 |          | oncurrency Library             |      |

|   |     | 6.4.1    | Our Library's API              |      |

|   |     | 6.4.2    | Deadlocks and Other Problems   |      |

|   |     | 6.4.3    | An STM Implementation          |      |

|   |     | 6.4.4    | Forking parallel threads       |      |

|   |     | 6.4.5    | Deterministic send and receive |      |

|   |     | 6.4.6    | A Mailbox Implementation       |      |

|   | 6.5 | Experi   | imental Results                |      |

|   |     | 6.5.1    | STM Versus Mailbox Rendezvous  | . 67 |

|   |     | 6.5.2    | Examples Without Rendezvous    |      |

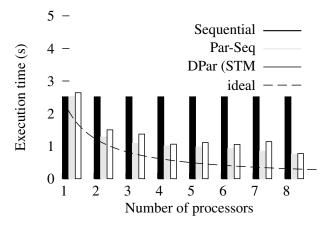

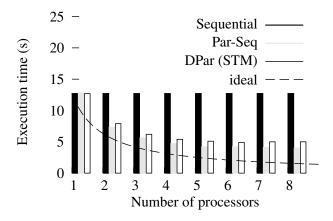

|   |     | 6.5.3    | Maximum element in a list      |      |

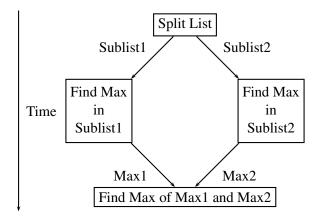

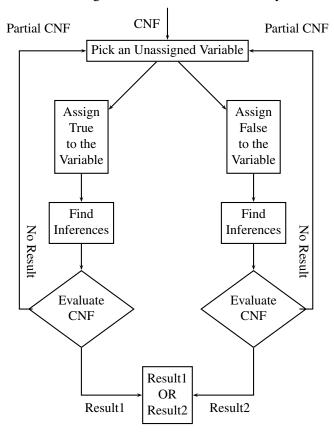

|   |     | 6.5.4    | Boolean Satisfiability         |      |

|   |     | 6.5.5    | Examples With Rendezvous       |      |

|   |     | 6.5.6    | Linear Search                  |      |

|   |     | 6.5.7    | Systolic Filter and Histogram  |      |

|   | 6.6 | Conclu   | usions                         |      |

|   |     |          |                                |      |

| Ш  | De     | eadlock-freedom                        | 77        |

|----|--------|----------------------------------------|-----------|

| 7  | Dead   | llock Detection with a Model Checker   | <b>79</b> |

|    | 7.1    | Related Work                           | 81        |

|    | 7.2    | Abstracting SHIM Programs              | 82        |

|    |        | 7.2.1 An Example                       | 84        |

|    | 7.3    | Modeling Our Automata in NuSMV         | 88        |

|    | 7.4    | Finding Deadlocks                      | 91        |

|    | 7.5    | Results                                | 91        |

|    | 7.6    | Conclusions                            | 93        |

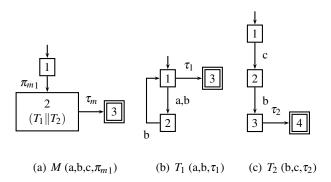

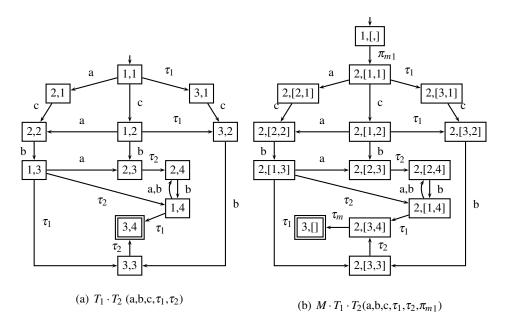

| 8  | Com    | positional Deadlock Detection for SHIM | 96        |

|    | 8.1    | An Example                             | 97        |

|    | 8.2    | Compositional Deadlock Detection       | 101       |

|    |        | 8.2.1 Notation                         | 101       |

|    |        | 8.2.2 Our Algorithm                    | 104       |

|    | 8.3    | Experimental Results                   | 105       |

|    | 8.4    | Related work                           | 110       |

|    | 8.5    | Conclusions                            | 113       |

| 9  | Run    | time Deadlock Detection for SHIM       | 114       |

|    | 9.1    | The Algorithm                          | 114       |

|    | 9.2    | Conclusions                            | 118       |

| 10 | $D^2C$ | A Deterministic Deadlock-free Model    | 120       |

|    | 10.1   | Approach                               | 120       |

|    | 10.2   | Implementation                         | 121       |

|    | 10.3   | Results                                | 122       |

|    |        | Conclusions                            | 124       |

|    |        |                                        |           |

| IV | Im     | proving Efficiency                     | 125       |

| 11 |        | icing Memory in SHIM programs          | 127       |

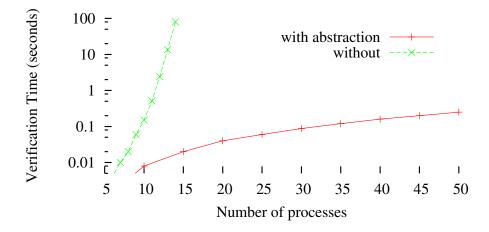

|    | 11.1   | Abstracting SHIM Programs              | 129       |

|    |        | 11.1.1 An Example                      | 129       |

|    |        | Merging Tasks                          | 133       |

|    |        | Tackling State Space Explosion         | 138       |

|    |        | Buffer Allocation                      | 139       |

|    | 11.5   | Experimental Results                   | 140       |

|    | 11.6   | Related Work                           | 141       |

|    | 11.7 Conclusions .        |                                               | 142                 |

|----|---------------------------|-----------------------------------------------|---------------------|

| 12 | <b>Optimizing Barrier</b> | Synchronization                               | 143                 |

|    |                           | amming Language                               |                     |

|    | 12.2 Clocks in X10        |                                               | 147                 |

|    | 12.2.1 Clock F            | Patterns                                      | 149                 |

|    | 12.3 The Static Anal      | lyzer                                         | 151                 |

|    | 12.3.1 Constru            | acting the Automaton                          | 152                 |

|    | 12.3.2 Handlin            | ng Async Constructs with the Clock Model      | 153                 |

|    | 12.3.3 Specify            | ring Clock Idioms                             | 153                 |

|    | 12.3.4 Combin             | ning Clock Analysis with Aliasing Analysis    | 154                 |

|    | 12.4 The Code Optin       | mizer                                         | 154                 |

|    | 12.5 Results              |                                               | 158                 |

|    | 12.6 Related Work         |                                               | 159                 |

|    | 12.7 Conclusions an       | d Future Work                                 | 160                 |

| 13 | <b>Optimizing Locks</b>   |                                               | 162                 |

|    | 13.1 Introduction .       |                                               | 163                 |

|    | 13.2 Flexible, Fixed      | -Owner Biased Locks                           | 166                 |

|    | 13.3 Transferring Ov      | wnership On-The-Fly                           | 168                 |

|    | 13.4 Mutual Exclusi       | on and Memory Fences                          | 169                 |

|    | 13.5 Asymmetric Lo        | ocks                                          | 171                 |

|    | 13.6 Read-Write Bia       | ased Locks                                    | 172                 |

|    | 13.7 Algorithm Veri       | fication                                      | 175                 |

|    | 13.8 Experimental R       | Results                                       | 176                 |

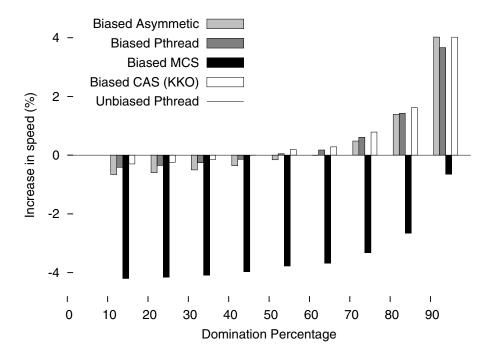

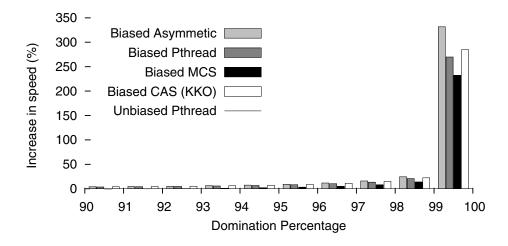

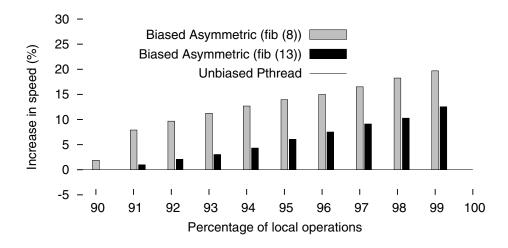

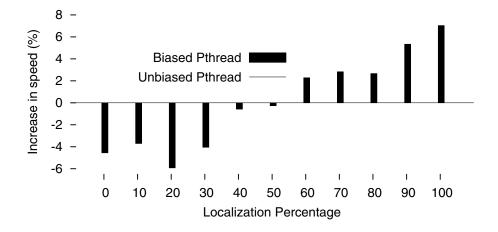

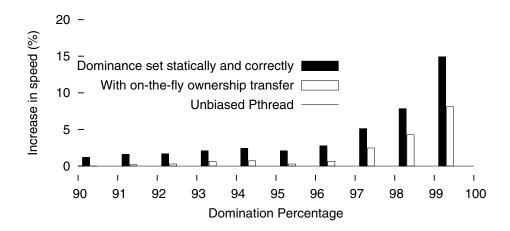

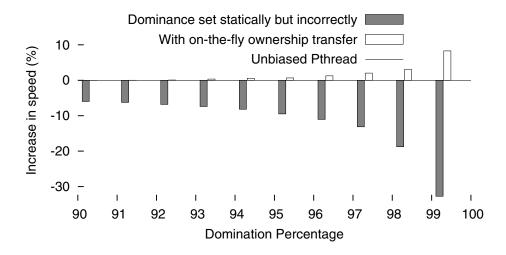

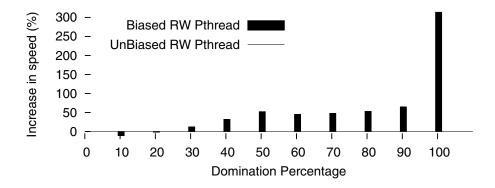

|    | 13.8.1 Perform            | nance with varying domination                 | 176                 |

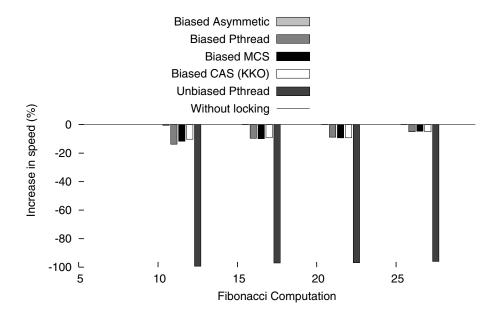

|    | 13.8.2 Locked             | vs. lockless sequential computation           | 182                 |

|    | 13.8.3 Perform            | nance of a packet-processing simulator with a | symmetric locks 182 |

|    |                           | Locks for Database Queries                    |                     |

|    | 13.8.5 Owners             | ship transfer                                 | 183                 |

|    |                           | ship transfer with incorrect dominance        |                     |

|    | 13.8.7 Overhe             | ads for nondominant behavior                  | 183                 |

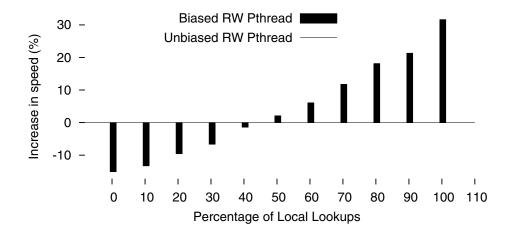

|    | 13.8.8 Perform            | nance of biased read-write locks              | 184                 |

|    | 13.8.9 Perform            | nance on a simulated router application       | 184                 |

|    | 13.9 Related Work a       | nd Conclusions                                | 184                 |

| V  | Conclusions               |                                               | 186                 |

| 14 | Conclusions               |                                               | 187                 |

Bibliography 188

# **List of Figures**

| 1.1  | A nondeterministic parallel program                         | 3  |

|------|-------------------------------------------------------------|----|

| 2.1  | Example of Kahn Processes                                   | 11 |

| 2.2  | Kahn network of Figure 2.1                                  | 11 |

| 2.3  | Two threads $T_1$ and $T_2$ running in parallel             | 13 |

| 4.1  | A concurrent SHIM program with communication and exceptions | 27 |

| 4.2  | Dependencies in JPEG decoding                               | 28 |

| 4.3  | Seven-task schedule for JPEG                                | 28 |

| 4.4  | SHIM code for the schedule in Figure 4.3                    | 30 |

| 4.5  | A pipelined schedule for JPEG                               | 30 |

| 4.6  | SHIM code for the JPEG schedule in Figure 4.5               | 31 |

| 4.7  | Shared data structures for tasks and channels               | 33 |

| 4.8  | C code for send A in function $h()$                         | 34 |

| 4.9  | C code for the <i>event</i> function for channel A          | 35 |

| 4.10 | C code for <i>throw Done</i> in function $j()$              | 35 |

| 4.11 | C code for calling $f()$ and $g()$ in $main()$              | 36 |

| 4.12 | C code in function $f()$ controlling its execution          | 37 |

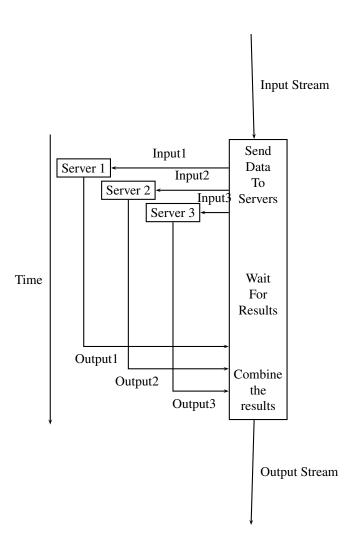

| 5.1  | The structure of the code our compiler generates            | 45 |

| 5.2  | Shared data for the <i>foo</i> task and <i>cin</i> channel  | 46 |

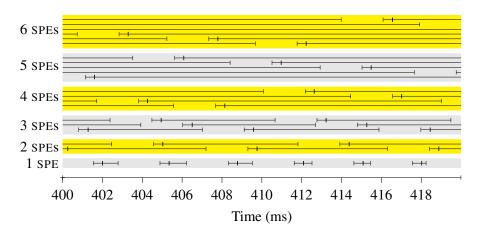

| 5.3  | Temporal behavior of the FFT for various SPEs               | 49 |

| 5.4  | Temporal behavior of the JPEG decoder                       | 49 |

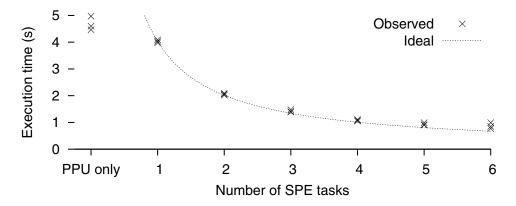

| 5.5  | Running time for the FFT on varying SPEs                    | 50 |

| 5.6  | Running time for the JPEG decoder on varying SPEs           | 51 |

| 6.1  | Using mailboxes in Haskell                                  | 57 |

| 6.2  | A Haskell program using STM                                 | 58 |

| 6.3  | A simple producer-consumer system using our library         | 58 |

| 6.4  | A two-stage pipeline in our library                         | 60 |

| 6.5  | The interface to our concurrency library                    | 61 |

| 6.6  | The channel type (STM)                                      | 61 |

| 6.7  | Creating a new channel (STM)                                      | 61    |

|------|-------------------------------------------------------------------|-------|

| 6.8  | Our implementation of dPar                                        | 62    |

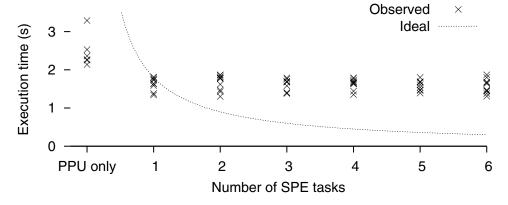

| 6.9  | The effects on <i>connections</i>                                 | 63    |

| 6.10 | A rendezvous among two readers and one writer                     | 64    |

| 6.11 | dSend (STM)                                                       | 64    |

| 6.12 | dRecv (STM)                                                       | 65    |

| 6.13 | The channel type (Mailboxes)                                      | 65    |

| 6.14 | newChannel (Mailboxes)                                            | 66    |

| 6.15 | dSend (Mailboxes)                                                 | 66    |

| 6.16 | dRecv (Mailboxes)                                                 | 67    |

| 6.17 | Calculating Fibonacci numbers with Haskell's par-seq              | 68    |

| 6.18 | Maximum Element in a List                                         | 69    |

| 6.19 | Structure of Maximum Finder                                       | 70    |

| 6.20 | Boolean Satisfiability                                            | 71    |

| 6.21 | Structure of the SAT Solver                                       | 71    |

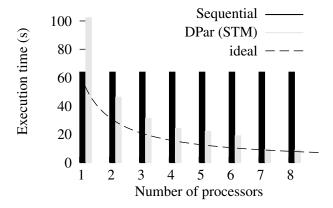

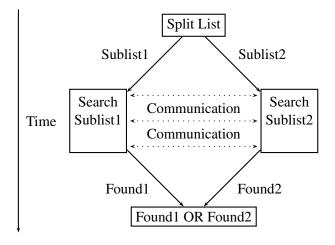

| 6.22 | Times for Linear Search                                           | 72    |

| 6.23 | Linear Search Structure                                           | 72    |

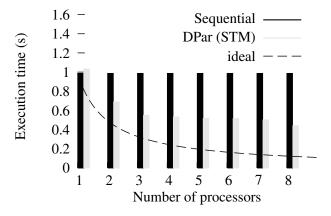

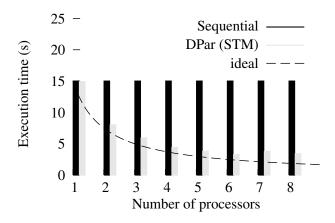

| 6.24 | Systolic Filter                                                   | 73    |

| 6.25 | RGB Histogram                                                     | 74    |

| 6.26 | Server Programming Style used by Histogram and Systolic Filter    | 75    |

| 7.1  | A SHIM program that deadlocks                                     | 79    |

| 7.2  | A deadlock-free SHIM program                                      | 82    |

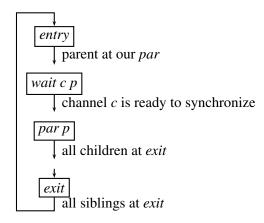

| 7.3  | The IR and automata for the example in Figure 7.2                 | 83    |

| 7.4  | The four types of automaton states                                | 84    |

| 7.5  | NuSMV code for the program in Figure 7.2                          | 87    |

| 7.6  | SHIM code and the conditions for rendezvous on channel $a$        | 90    |

| 7.7  | The JPEG decoder fragment that causes our tool to report a deadle | ck 93 |

| 7.8  | An equivalent version of the first task in Figure 7.7             | 94    |

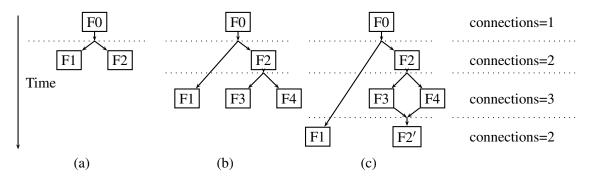

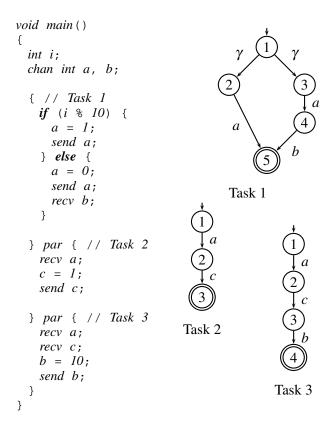

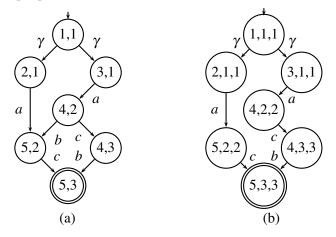

| 8.1  | Analyzing a four-task SHIM program                                | 98    |

| 8.2  | A SHIM program and the automata for its tasks                     | 99    |

| 8.3  | Composing automata                                                | 100   |

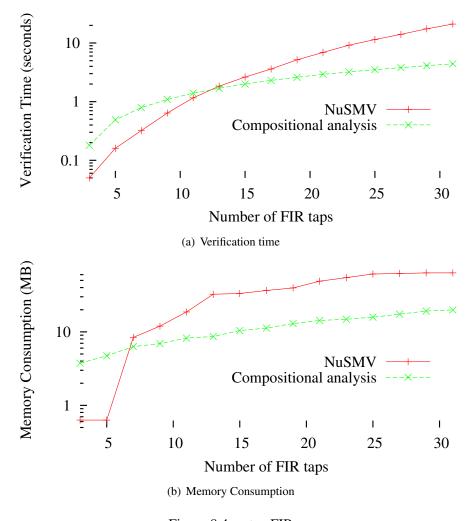

| 8.4  | n-tap FIR                                                         | 106   |

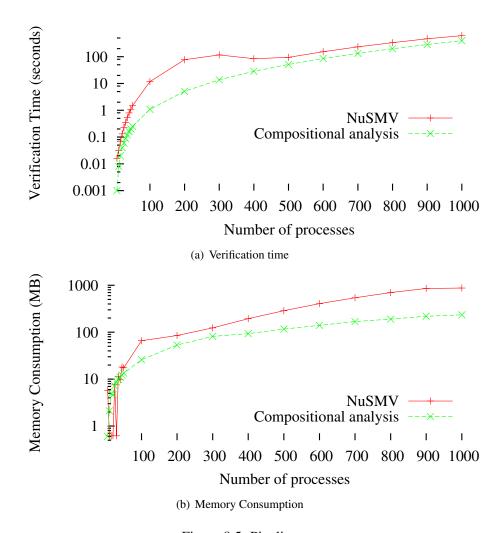

| 8.5  | Pipeline                                                          | 107   |

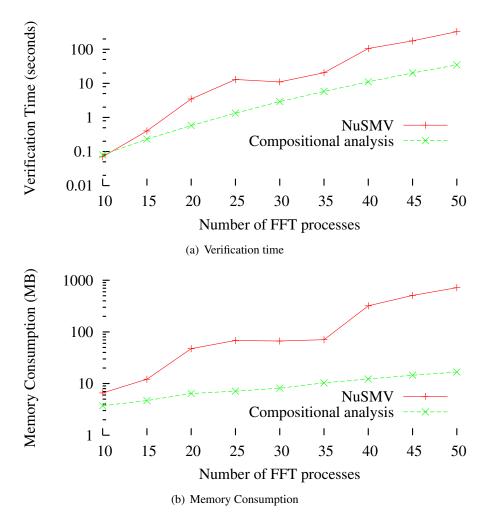

| 8.6  | Fast Fourier Transform                                            | 108   |

| 8.7  | JPEG Decoder                                                      | 109   |

| 8.8  | Verification times for the <i>n</i> -task pipeline                | 111   |

| 8.9  | A SHIM program's call graph                                       | 111   |

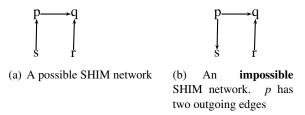

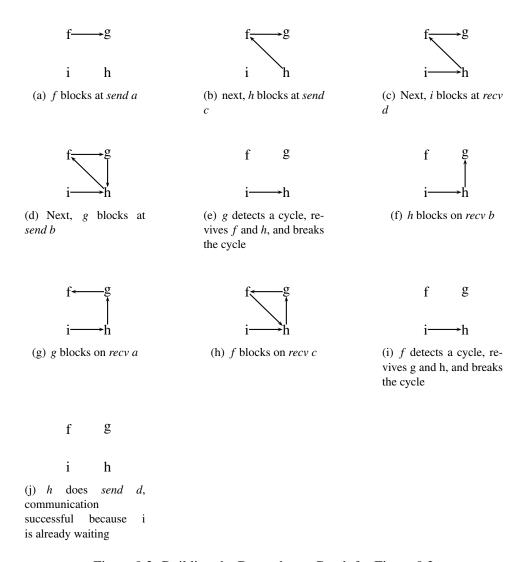

| 9.1<br>9.2<br>9.3                                                    | Possible and impossible configurations of tasks in the SHIM mode<br>Another example of the effect of our deadlock-breaking algorithm<br>Building the Dependency Graph for Figure 9.2                                                                                                                                                             |                                                             |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

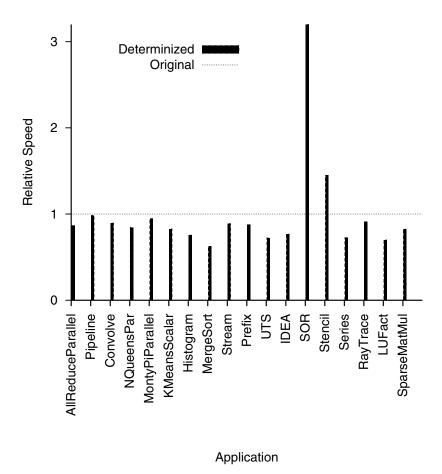

| 10.1<br>10.2                                                         | A $D^2C$ program                                                                                                                                                                                                                                                                                                                                 | 121<br>123                                                  |

| 11.1<br>11.2<br>11.3<br>11.4                                         | A SHIM program that illustrates the need for buffer sharing  A SHIM program                                                                                                                                                                                                                                                                      | 128<br>130<br>131<br>132                                    |

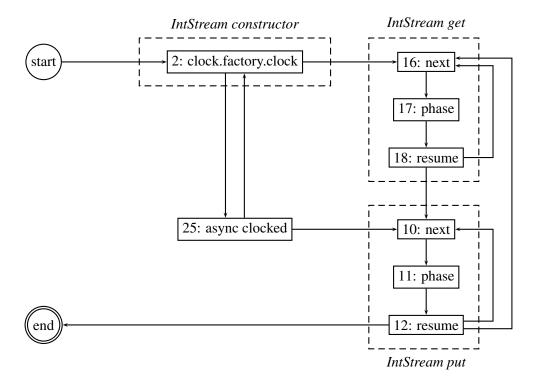

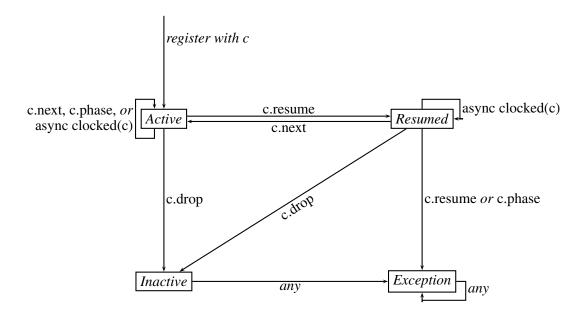

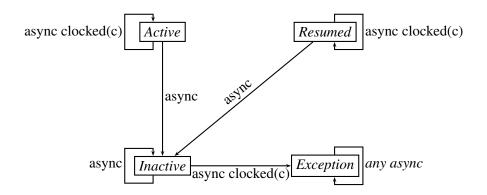

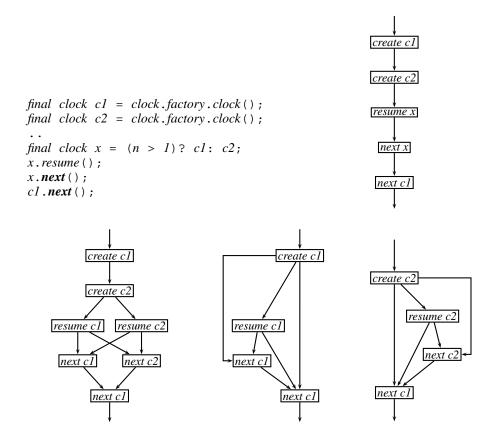

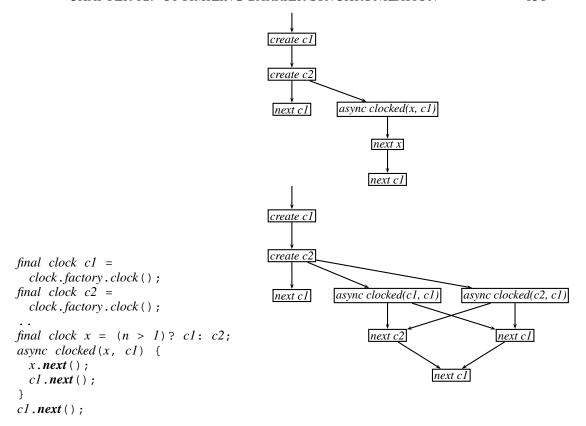

| 12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8<br>12.9 | A program to compute Pascal's Triangle in X10 using clocks Automaton for the clock in the Pascal's Triangle example The clock API The state of one activity with respect to clock c Modeling async calls Additional transitions in the clock state Aliasing clocks in X10 Asyncs and Aliases Various implementations of next and related methods | 145<br>146<br>149<br>150<br>152<br>153<br>155<br>156<br>157 |

| 13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.6                         | A spin lock using atomic compare-and-swap Our general biased-lock scheme                                                                                                                                                                                                                                                                         | 163<br>167<br>168<br>169<br>173<br>174                      |

| 13.7<br>13.8<br>13.9<br>13.10                                        | Write functions of biased read-write locks                                                                                                                                                                                                                                                                                                       | 175<br>177<br>178<br>178                                    |

| 13.11<br>13.12<br>13.13<br>13.14<br>13.15                            | Behavior of our packet-processing simulator with asymmetric lock Performance of our biased locks on a database simulator The effect of bias transfer                                                                                                                                                                                             | ts 179<br>179<br>180<br>180<br>181                          |

| 13.16<br>13.17                                                       | A comparison of our biased rwlock with Linux thread rwlock Performance of our biased read-write locks on a router simulator                                                                                                                                                                                                                      | 181<br>182                                                  |

# **List of Tables**

| 1.1  | Thesis outline                                                | 6   |

|------|---------------------------------------------------------------|-----|

|      | Experimental Results for the JPEG decoder                     |     |

| 6.1  | Time to rendezvous for STM and Mailbox implementations        | 68  |

| 7.1  | Experimental results with NuSMV                               | 90  |

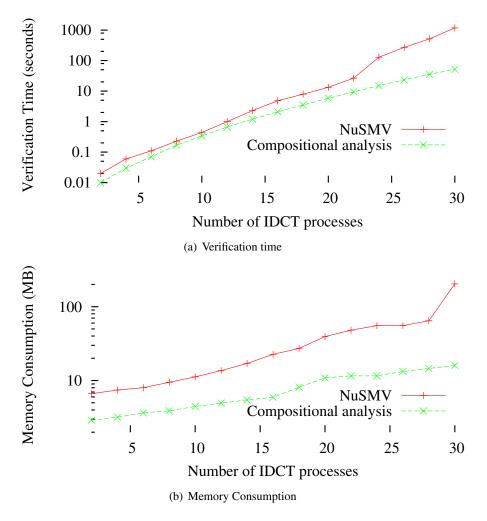

| 8.1  | Comparison between compositional analysis (CA) and NuSMV $$ . | 103 |

|      | Experimental results with the threshold set to 8000           |     |

| 12.1 | Experimental Results of our clock specialization              | 158 |

# Acknowledgments

Here is my consolidated list of people I would like to thank:

- Stephen Edwards (Columbia University)

I would like to foremost thank my advisor, who did a perfect mix of micro and macro managing and at perfect times. Without his constant encouragement, I would not have been able to start and complete my thesis. I owe a major part of my success to Stephen.

- Alfred Aho, Luca Carloni, Martha Kim (Columbia University)

I can best describe them as 'easily approachable'. Not only did they serve on my thesis committee, but they also never denied when I asked for recommendations.

- Julian Dolby, Vijay Saraswat, Olivier Tardieu (IBM Research)

A major part of my ideas towards my thesis originated at IBM. I would like to thank them for their guidance and providing me with the right infrastructure.

- Kedar Namjoshi (Bell Laboratories)

I would like to thank Kedar for his expertise and guidance in theoretical concepts without which I would have felt incomplete.

- Satnam Singh (Microsoft Research)

The biggest stepping stone of my thesis was my first paper with Satnam.

I would like to thank him for sponsoring me a paid vacation to the United Kingdom and also for serving on my thesis.

- Prakash Shankor, Saraswathi Vasudevan, Vasudevan Venkataraman (My family)

I blame Prakash for igniting the idea of PhD in my head and letting me do what I wanted to. I owe the entire non-technical part of my thesis to him. I finally thank my parents for letting me fulfil their wishes.

# Part I Introduction

## **Chapter 1**

## The Problem

Multicore shared-memory multiprocessors now rule the server market. While such architectures provide better performance per watt, they present many challenges.

Scheduling—instruction ordering—is the biggest issue in programming shared-memory multiprocessors. While uniprocessors go to extremes to provide a sequential execution model despite caches, pipelines, and out-of-order dispatch units, multiprocessors typically only provide such a guarantee for each core in isolation; instructions are at best partially ordered across core boundaries.

Controlling the scheduling on multiprocessors is crucial not only for performance, but because data races can cause scheduling choices to change a program's function. Worse, the operating system schedules nondeterministically.

We say that a program produces nondeterministic output if it is capable of producing different outputs during reruns of the program with the same input. The program in Figure 1 is nondeterministic. It uses C++-like semantics with Cilk [19]-like constructs for concurrency. It creates two tasks f and g in parallel using the *spawn* construct. Both functions take x by reference. Clearly, x is getting modified concurrently by both the tasks, so the value printed by this program is either 3 or 5 depending on the schedule. One way to avoid races is to protect x by a lock and thereby ensure atomic updates to x, but this still gives nondeterministic output. This is because operations within atomic blocks are not commutative.

Such nondeterministic functional behavior arising from timing variability—a data race—is among the nastiest things a programmer may confront. It makes debugging all but impossible because unwanted behavior is rarely reproducible [11]. Rerunning a nondeterministic program on the same input usually does not produce the same behavior. Inserting assert or print statements or running the program in a debugger usually changes timing enough to make the bug disappear. Debugging such programs is like trying to catch a butterfly that is only visible from the corner

```

void f(int &a) {

a = 3;

}

void g(int &b) {

b = 5;

}

main() {

int x = 1;

spawn f(x)

spawn g(x);

sync; /* Wait for f and g to finish */

print x;

}

```

Figure 1.1: A nondeterministic parallel program

of your eye.

We believe a programming environment should always provide functional determinism because it is highly desirable and is very difficult to check for on a per-program basis. Virtually all sequential programming languages (e.g., C) are deterministic: they produce the same output given the same input. Inputs include usual things such as files and command-line arguments, but for reproducibility and portability, things such as the processor architecture, the compiler, and even the operating system are not considered inputs. This helps programmers by making it simpler to reason about a program and it also simplifies verification because if a program produces the desired result for an input during testing, it will do so reliably.

By contrast, concurrent software languages based on the traditional shared memory, locks, and condition variables model (e.g., pthreads or Java) are not deterministic by this definition because the output of a program may depend on such things as the operating system's scheduling policy, the relative execution rates of parallel processors, and other things outside the application programmer's control. Not only does this demand a programmer consider the effects of these things when designing the program, it also means testing can only say a program *may* behave correctly on certain inputs, not that it will.

A few concurrent programming languages provide determinism through semantics. SHIM [47; 116] is one such instance. It is an asynchronous concurrent language that is scheduling independent: its input/output behavior is not affected by any nondeterministic scheduling choices taken by its runtime environment due

to processor speed, the operating system, scheduling policy, etc. A SHIM program is composed of sequential tasks that synchronize whenever they want to communicate. The language is a subset of Kahn networks [70] (to ensure determinism) that employs the rendezvous of Hoare's CSP [62] for communication to keep its behavior tractable.

Kahn's unbounded buffers would make the language Turing complete, even with only finite-state processes, so the restriction to rendezvous makes the language easy to analyze. Furthermore, since SHIM is a strict subset of Kahn networks, it inherits Kahn's scheduling independence: the sequence of data values passed across each communication channel is guaranteed to be the same for all correct executions of the program (and potentially input dependent).

The central hypothesis of SHIM is that deterministic concurrent languages are desirable and practical. That they relieve the programmer from considering different execution orders is clear; whether they impose too many constraints on the algorithms they can express is also something we attempt to answer here.

Although SHIM is deterministic, it is not deadlock free; a programmer may use language constructs incorrectly to cause the program to deadlock. We demonstrate that deadlocks can be easily detected statically because of the deterministic property of SHIM.

Our ultimate goal is to have both determinism as well as deadlock freedom. In the next section, we discuss the terms used in this thesis followed by the problem we are addressing. Then, we discuss some of things to remember while designing deterministic, deadlock free systems. Finally, we give an outline of this thesis.

#### 1.1 Terminology

This section defines the terms used in this thesis.

A *multi-core processor* is a system that consists of two or more cores. Multicores are used for reduced power consumption and simultaneous processing of multiple tasks, therefore resulting in enhanced performance. A *task* or a *process* is a sequential unit of computation. A *sequential program* has a single task. By contrast, a *parallel program* consists of multiple tasks that may execute concurrently.

A *programming model* is an abstraction or a template to express algorithms. *Programming languages* are more concrete and are based on programming models. They have specific forms of syntax and semantics.

An *application* is an instance of a sequential or parallel program that implements an algorithm in a programming language. A *benchmark* is a set of standard applications used to assess the performance of something, usually by running a number of standard tests.

#### 1.2 Problem Statement

This thesis wishes to provide programming language support for the following:

- **Determinism**: By determinism, we mean that the output of a program depends only on the input of the program and not on the running environment. Inputs include things such as files and command-line arguments. We do not deal with reactive systems. Programming environment includes things such as the processor architecture, compiler, and even the operating system and these are not considered inputs.

- Deadlock-freedom: A deadlock is a situation in which two or more tasks

wait for each other to make progress, but neither ever does causing an indefinite wait. A deadlock usually arises because of improper synchronization.

We require techniques to detect and avoid these situations. We do not wish

to solve the termination problem.

#### 1.3 Design Considerations

While we design a deterministic and a deadlock-free system, our goal is to achieve three things: performance, scalability and programmer flexibility.

#### 1.3.1 Performance

A general hypothesis is that determinism introduces performance degradation because of synchronization. There are two types of synchronization: centralized and distributed. A centralized synchronization forces all tasks in a system to synchronize while a distributed synchronization forces only a subset of tasks to synchronize. Distributed methods perform better because the tasks have to wait less, but they are more susceptible to deadlocks. An out-of-order synchronization between subsets of tasks may lead to a deadlock. On the other hand, in centralized systems, deadlocks are avoided because all tasks are forced to synchronize at the same point.

In some cases, the programming environments are nondeterministic, but there are techniques and tools to check for determinism and deadlocks during runtime. The problem with these tools is that they add a considerable amount of overhead that reduces performance drastically.

| Part               | Chapter | Question to answer                            | Published              |

|--------------------|---------|-----------------------------------------------|------------------------|

|                    | 3       | How can we achieve determinism?               | SES 2010 [50]          |

| II                 | 4       | Is determinism efficient?                     | DATE 2008 [51]         |

| (Determinism)      | 5       | Is determinism practical?                     | SAC 2009 [124]         |

|                    | 6       | Determinism: Language vs. Library?            | IPDPS 2008 [130]       |

| III                | 7       | How do we solve the deadlock problem?         | MEMOCODE 2008 [122]    |

| (Deadlock-freedom) | 8       | How can we efficiently detect deadlocks?      | EMSOFT 2009 [109]      |

|                    | 9       | How can we deterministically break deadlocks? | HOTPAR 2010 [127]      |

|                    | 10      | How can we enforce deadlock freedom?          | HIPC-SRS 2010 [128]    |

| IV                 | 11      | Can we reduce memory in deterministic         | MEMOCODE 2009 [123]    |

| (Efficiency)       |         | programs?                                     | TCAD 2010 [126]        |

|                    | 12      | Can we optimize deterministic constructs?     | CC 2009 [131]          |

|                    | 13      | Can we optimize locks?                        | PACT 2010 [129]        |

| V                  | 14      | What are the limitations?                     | IPDPS Forum 2008 [125] |

| (Conclusions)      |         | What next?                                    | PLDI-FIT 2009 [125]    |

Table 1.1: Thesis outline

#### 1.3.2 Scalability

A number of programming environments provide determinism at compile time. Static verifiers and type systems are examples of such environments. These techniques do not explicitly introduce deadlocks but they do not scale at compile time because they have to consider all possible interleavings of tasks in the program.

Among the systems that provide determinism at runtime, distributed systems are known to scale better than centralized systems in both performance and ease of implementation.

#### 1.3.3 Programmer Flexibility and Ease of Use

Most deterministic programming models provide determinism by imposing a number of restrictions. Most type systems require programmers to explicitly annotate the program. Static verifiers do not force any restrictions on the program, but they simply do not scale with flexible programs and give false positives as results. Our goal is to achieve a balance between performance, scalability and programmer flexibility.

#### 1.4 Thesis Outline

Table 1.1 gives the overview of this thesis. We first provide a background study in Chapter 2. We then begin by describing the SHIM model in Part II. We evaluate our model by generating code for different architectures. We illustrate a backend in Chapter 4 for SHIM that generates C code that made calls to the POSIX thread

(pthread) library to ask for parallelism. Each communication acquires the lock on a channel and checks whether every process connected to it also had blocked (i.e., whether the rendezvous could occur).

We also illustrate a backend for IBM's CELL processor in Chapter 5. A direct offshoot of the pthread backend, it allows the user to assign computationally intensive tasks to the CELL's synergistic processing units (SPUs); remaining tasks run on the CELL's PowerPC core (PPU).

Next, we illustrate the feasibility of SHIM as a library. We provide a deterministic concurrent communication library in Chapter 6 for an existing multithreaded language. We implemented the SHIM in the Haskell functional language, which supports transactional memory.

SHIM is interesting because it is deterministic but it is not deadlock free. We provide simple techniques to detect deadlocks in SHIM in Part III. SHIM does not need to be analyzed under an interleaved model of concurrency since most properties, including deadlock, are preserved across schedules. In Chapter 7, we use a synchronous model checker NuSMV [34] to detect deadlocks in SHIM—a surprising choice since SHIM's concurrency model is fundamentally asynchronous. We later take a compositional approach in Chapter 8 in which we build an automaton for a complete system piece by piece. The result: our explicit model checker outperforms the implicit NuSMV on these problems. Our evaluations led to other directions. We wanted a more robust concurrent programming model that is both deterministic and deadlock free – we discuss the  $D^2C$  model in Chapter 10.

We then provide a few optimization techniques to improve the efficiency of SHIM and other related languages like X10 [29] in Part IV. To improve the efficiency of the SHIM model, we applied model checking to search for situations where buffer memory can be shared [123; 126]. In general, each communication channel needs its own space to store any data being communicated over it. However, in certain cases, it is possible to prove that two channels can never be active simultaneously and thus share buffer memory.

In Chapter 12, we describe a tool that mitigates the overhead of general-purpose clocks in IBM's X10 language by analyzing how programs use the clocks and then by choosing optimized implementations when available. These clocks are deterministic barriers and are similar to SHIM's communication constructs.

The major bottleneck of deterministic programs is due to synchronization. Synchronization constructs are implemented using low level locks. In Chapter 13, we describe efficient locking algorithms for specialized locking behavior.

Finally, we discuss the limitations of SHIM in Chapter 14. We report our conclusions and open new directions for future work.

## **Chapter 2**

# **Background**

Concurrent programming languages suffer from a number of problems including nondeterminism and deadlocks. This chapter surveys the various issues involved while designing concurrent systems and particularly focuses on techniques that deal with nondeterminism and deadlocks. We provide a survey of the various programming models, tools and techniques that are in use today to build concurrent systems, and specifically how they address deadlock and nondeterminism problems at various levels — compiler, programming language, operating systems and hardware.

#### 2.1 Problems with concurrent programming

Concurrency comes with an abundant number of problems. We list a few below.

- **Paradigm shift:** Sequential computers were ruling the world but not anymore. Most programmers find concurrency hard because they are trained to think sequentially.

- Lack of a good model: There is no widely accepted concurrent programming or memory model. The next section surveys the programming models that are in use today and discusses their pros and cons.

- Concurrency bugs: Bugs like nondeterminism and deadlocks that are virtually absent in sequential programming are exposed in concurrent programming. We list some of the concurrency bugs here:

- Nondeterminism: A condition when some possible interleaving of tasks results in undesired program output.

- Deadlock: A state in which two or more tasks indefinitely wait for each other.

- No Fairness: A condition when some task does not get a fair turn to make progress.

- Starvation: A state when a task is deprived of a shared resource forever.

- **Portability:** Programmers are generally required to have knowledge about the underlying layers(no. of cores, operating system scheduling policy, cache size and policy, memory layout and other hardware features) to produce efficient concurrent programs. Therefore, a program written for one architecture may not be suitable for another architecture resulting in poor portability. Also, with emerging and changing architectures, programs may have to be rewritten to suit different architectures.

This thesis mainly addresses nondeterminism and deadlocks, although we believe that all the issues listed are equally important. We also try not to neglect these issues while designing deterministic and deadlock-free systems.

#### 2.2 Concurrent programming models

Concurrent programming models are becoming more prominent with the advent of multicore systems. They provide a layer of abstraction between the application and the underlying architecture including the operating system. A programming model may choose to hide or expose aspects of the operating system and hardware. Specifically, a concurrent programming model controls the concurrency features provided by the operating system or hardware.

Generally, the more the model exposes, the more efficient code can a programmer write. As a consequence of more exposure, the programmer has to explicitly work with the lower layers and therefore, productivity is reduced. He is also exposed to a number of bugs like nondeterminism and deadlocks, since he has access to lower layers.

Alternatively, a programming model may choose to expose very little of the underlying layers and hence release the programmers the burden of dealing with low level details that include the operating system and hardware. Such a model may also hide low level bugs, thereby allowing programmers to deal with bug-free code. The SHIM model is an instance of this kind of programming model. It abstracts away nondeterminism from the programmer.

The SHIM model forces synchronization of tasks while accessing shared data to provide determinism. The model eliminates data races by design and also simplifies the deadlock detection process. Tasks in SHIM can be created in parallel using

the *par* statement. It uses message-passing-like semantics for communication. We discuss the model in detail in the next chapter.

Message passing is a well known approach used by parallel tasks to communicate with each other and works well for distributed systems. The Message Passing Interface (MPI) is a popular standard library for creating and communicating between concurrent threads. The communication pattern is flexible (blocking, unblocking, variable buffer size) and easily programmable. MPI was not designed to deal with issues such as nondeterminism and deadlocks; the programmer has to deal with these issues explicitly.

CSP (Communicating Sequential Processes)[61] is another parallel programming model that uses message passing. The communication is blocking – both the sender and the receiver have to rendezvous for the communication to be successful. A task may choose to wait on two or more channels at the same time, and resume execution as soon as data is available on one of the channels. This makes the output dependent on time, making the model nondeterministic.

By contrast, a Kahn network is a deterministic concurrent programming model that uses message passing for communication. A Kahn Network [70] is composed of a set of communication processes that may send and receive on channels. Each communication channel connects a single sending process with a single receiving process. The communication structure of a system is therefore a directed graph whose nodes are processes and whose arcs are channels. There is no shared data; processes communicate only through channels. The receiver process is blocking: it waits until the sender writes the data. The receiver cannot choose to wait based on whether the data is available or not. This property makes the model deterministic. The sender is nonblocking; it writes to one end of the channel and the receiver reads from the other end. The channel is implemented as an unbounded buffer.

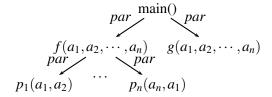

Figure 2.1 is an example of a Kahn processes and its corresponding network is shown in Figure 2.2. f, g and h are three parallel tasks created by the par construct in main(). The two producer tasks f and g send values 1 (on channel a) and 0 (on channel b) respectively. Task h receives the values from channels a and b into variable j. j sees an alternating stream of 1's and 0's.

In Figure 2.1, suppose f runs faster than g or h, then the channel a fills in quickly. However, h will not be able to receive the data as quickly as f sends. Therefore, there will be an accumulation of data on the channel. This is not a problem in Kahn's model, because the channel acts as an infinite queue between the producer and the consumer.

In practice, this infinite bound is impossible to implement. The SHIM model provides functional determinism by adopting Kahn networks, and also solves the unbounded buffer problem by using CSP-style rendezvous for communication. The sender and the receiver have to wait for each other to communicate data.

```

void f(out a)

for(;;) {

send a = 1; /* sends 1 on channel a */

}

void g(out b)

for(;;) {

send b = 0; /* sends 0 on channel b */

}

void h(in a, in b) {

int j;

for (int i = 0; i++;)

if (i%2)

j = recv \ a; /* receives 1 */

j = recv \ b; /* receives 0 */

}

}

main() {

chan int a, b;

f(a) par g(b) par h(a, b); /* Runs the three tasks in parallel */

```

Figure 2.1: Example of Kahn Processes

Figure 2.2: Kahn network of Figure 2.1

Concurrent programming models also control the mode of parallelism and it can be broadly classified into two types: data level parallelism and task level parallelism. Data level parallelism forces parts of data to be distributed over different processors and computed concurrently. A classic example is allowing different elements of an array to be processed concurrently. By contrast, task level parallelism is allowing code to run concurrently. For instance, SHIM supports task level parallelism.

Programming models also restrict the class of applications that can be implemented. MIT's StreamIt [119] model, for example, is primarily suitable for stream processing applications. Stream computing has various applications including image and single processing. It is based on synchronous data flow [76] that operates on streams of data known as tokens. These tokens pass through a number of computation units known as filters. Filters communicate with each other through channels. Channels are implemented as buffers and pass tokens. StreamIt programs have single input and single output filters. Filters use *push*, *pop* and *peep* functions to operate on input and output streams. Streams can be pipelined. They can also be split and joined for data level parallelism.

StreamIt is completely deterministic. It has simple static verification techniques for deadlock and buffer overflow. However, StreamIt is a strict subset of SHIM and StreamIt's design limits it to a smaller class of applications.

By contrast, Cilk [19] is a an interesting programming language that it covers a larger class of applications. It is C based and the programmer must explicitly ask for parallelism using the *spawn* and the *sync* constructs. Cilk is definitely more expressive than SHIM and StreamIt. However, Cilk allows data races. Figure 1, for example, is a nondeterministic concurrent program in Cilk. Explicit techniques [30] are required for checking data races in Cilk programs.

X10 [29; 106] is another language that adopts the Cilk model. It uses *async* and *finish* instead of *spawn* and *sync*. It is a parallel and distributed object-oriented language. To a Java-like sequential core it adds constructs for concurrency and distribution through the concepts of *activities* and *places*. An activity is a unit of work, like a thread in Java, and is created by an *async* statement; a place is a logical entity that contains both activities and data objects.

Just like Cilk, the X10 language allows races and does not impose hard restrictions on how activities should be created. We describe the language in detail in Chapter 12.

Synchronous programming languages like Esterel [17] are deterministic. An Esterel program executes in clock steps and the outputs are synchronous with its inputs. Although an Esterel program is susceptible to causality problems, this form of deadlock can be detected at compile time. Unfortunately, synchronous models require constant, global synchronization and force designers to explicitly

schedule virtually every operation. Although standard in hardware designs, global synchronization is costly in software. Furthermore, the presence of a single global clock effectively forces entire systems to operate at the same rate. Frustration with this restriction was one of the original motivations for SHIM.

#### 2.3 Determinizing tools

A number of tools provide determinism. For example, Kendo is a software system that deterministically multithreads concurrent applications. Kendo [93] ensures a deterministic order of all lock acquisitions for a given program input. Consider two threads,  $T_1$  and  $T_2$  in Figure 2.3. Suppose x is initialized to 0, then the final value of x is either 1 or 2, depending on which thread acquires the lock first. Kendo removes this nondeterministic behavior by deterministically ordering the acquisition of locks. An example of deterministic ordering is lowest thread id first. In this case, Kendo waits for all threads to contend for the lock, then forces  $T_1$  to acquire the lock before  $T_2$ , thereby always giving the final value of x as 2.

```

Thread T_1 Thread T_2

lock(m); lock(m);

x++; x*=2;

unlock(m); unlock(m);

```

Figure 2.3: Two threads  $T_1$  and  $T_2$  running in parallel

Kendo comes with three shortcomings. It operates completely at runtime, and there is a considerable performance penalty. Secondly, if we have the sequence lock(A); lock(B) in one thread and lock(B); lock(A) in another thread, a deterministic ordering of locks may still deadlock. Thirdly, the tool operates only when shared data is protected by locks.

Software Transactional Memory (STM) [110] is an alternative to locks: a thread completes modifications to shared memory without regard for what other threads might be doing. At the end of the transaction, it checks for conflict freedom and commits if the validation was successful, otherwise it rolls back and re-executes the transaction. STM mechanisms avoid races but do not solve the nondeterminism problem.

Berger's Grace [16] is a runtime tool that is based on STM. If there is a conflict during commit, the threads are committed in a particular sequential order (determined by the order in which they appear in the source code), ensuring determinism. For instance, for the code in Figure 1, f commits before g, therefore resulting in output value 5. Grace works on Cilk programs. The tool ensures that the output

of the concurrent code is same as its sequential equivalent, and this sequential equivalent is obtained by removing *spawn* and *sync* statements from the concurrent program.

The problem with Grace is that it incurs a lot of runtime overhead. This dissertation partially solves this overhead problem by addressing the issue at compile time and thereby reducing a considerable amount of runtime overhead.

Like Grace, Determinator[6] is another tool that allows parallel processes to execute as long as they do not share resources. If they do share resources and the accesses are unsafe, then the operating throws an exception (a page fault).

Cored-Det [15], based on DMP [42] uses a deterministic token that is passed among all threads. A thread to modify a shared variable must first wait for the token and for all threads to block on that token. DMP is hardware based. Although, deadlocks may be avoided, we believe this setting is nondistributed because it forces all threads to synchronize and therefore leads to a considerable performance penalty. In the SHIM setting, only threads that share a particular channel must synchronize on that channel; other threads can run independently.

Deterministic replay systems [31; 5] facilitate debugging of concurrent programs to produce repeatable behavior. They are based on record/replay systems. The system replays a specific behavior (such as thread interleaving) of a concurrent program based on records. The primary purpose of replay systems is debugging; they do not guarantee determinism. They incur a high runtime overhead and are input dependent. For every new input, a new set of records is generally maintained.

Like replay systems, Burmin and Sen [23] provide a framework for checking determinism for multithreaded programs. Their tool does not introduce deadlocks, but their tool does not guarantee determinism because it is merely a testing tool that checks the execution trace with previously executed traces to see if the values match. Our goal is to guarantee determinism at compile time – given a program, it will generate the same output for a given input.

#### 2.4 Model checkers and verifiers

There are a number of model checkers that verify concurrent programs. SPIN [63], for instance, supports modeling of asynchronous processes. Properties to be verified are given as Linear Temporal Logic (LTL). SPIN expands all possible interleavings to verify a concurrent program. It is a general purpose tool and can be used to verify concurrent programs for properties including determinism and deadlocks. The problem with model checkers is that they do not scale to large programs. Also, they cannot express programs with complex structures and behaviors.

15

Martin Vechev's tool [132] finds determinacy bugs in loops that run parallel bodies. It analyzes array references and indices to ensure that there are no readwrite and write-write conflicts.

Type and effect systems like DPJ [20] have been designed for deterministic parallel programming. These systems do not themselves introduce deadlocks, but type systems generally require programmer annotations. SHIM does not require annotations; it provides restrictions through its constructs. One may argue against learning a new programming paradigm or language like SHIM, but SHIM can be implemented as a library (Chapter 6) and the deadlock detector (Part III) can be incorporated into it. The second problem with annotation based systems is that the programmer has to ensure correct annotation; otherwise it results in incorrect effect propagations.

# Part II Determinism

#### **Outline**

This part illustrates techniques to guarantee input-output determinism. We use a combination of compile-time and runtime techniques to obtain scheduling-independent behavior. Our approach is a deterministic programming model and language – SHIM. We start by explaining SHIM and its semantics. We then provide ways to generate efficient runtime code from SHIM programs for different architectures. We finally provide a deterministic concurrent library in Haskell that adopts the SHIM model for race-free behavior.

## Chapter 3

## The SHIM Model

Because of the popularity of multicore chips, there is a growing need for programming techniques, models, and languages that help exploit parallel hardware. In this chapter, we describe the concurrency model underlying a programming language called SHIM—"software/hardware integration medium" [116] for its initial bias toward embedded system applications—to ease the transition from single-threaded software to robust multicore-aware implementations.

One of the key features of SHIM is that the output behavior of a program is deterministic: the output of a program just depends on its input; it does not depend on the environment such as compiler, runtime, OS, or hardware platform. Concurrent tasks in SHIM run asynchronously and do not share any data. The environment may schedule the tasks in any way (i.e., different schedules produce different interleavings of the tasks), but still the program will produce deterministic output. If the tasks have to share data, they have to synchronize using rendezvous communication, and the SHIM's runtime system takes care of this. By rendezvous, we mean that all tasks sharing a particular variable have to meet – in a way similar to a barrier.

The deterministic property of SHIM simplifies validation. Most programs are still validated by simply running them. It is hard enough to validate a deterministic, sequential program with such an approach: the user must create an appropriate set of test cases and check the results of running the program on these cases. If the model is nondeterministic, as with most concurrent formalisms, even running a program on a test case only tells us what the result of running the program might be. It does not guarantee that the result is correct. A different testing environment may cause the program to behave differently for the same input. This is not the case with SHIM because it guarantees scheduling independence.

The SHIM model and language [47; 115] prevent data races by providing

scheduling independence: given the same input, a program will produce the same output regardless of what scheduling choices its runtime environment makes. It provides certain program correctness guarantees and makes others easy to check by adopting CSP's rendezvous [62] in a Kahn network [70] setting. In particular, SHIM's scheduling independence makes other properties easier to check because they do not have to be tested across all schedules; one is enough. Deadlock is one such property: for a particular input, a program will either always or never deadlock; scheduling choices (i.e., different interleaving of tasks) cannot cause or prevent a deadlock.

SHIM [116] is a C-like language with additional constructs for communication and concurrency. Specifically, p par q runs statements p and q in parallel, waiting for both to terminate before proceeding;  $send\ c$  and  $recv\ c$  are blocking communication operators that synchronize on a variable (or a channel) c. As an alternative to send and recv,  $next\ c$  is a blocking communication operator that synchronizes on channel c and either sends or receives data depending on which side of an assignment (=) the next appears.

SHIM tasks communicate exclusively through this multiway rendezvous; there are no global variables or pointers. Any variable that is shared should be a channel and be declared as *chan*. We illustrate SHIM with examples taken from Tardieu's paper [117].

Here, the program runs two tasks f and g concurrently. a and b are incarnations of channel c. In f, a is a copy of c that is first modified by a=3 before being updated by recv. By contrast, b is an alias for c in g, so the assignment b=5 actually modifies c. Because they are associated with the same variable, the send and recv operations must synchronize to execute. When they do, the recv statement copies the master value of a-c, which was set to s in s to the local copy of s. Thus s is s just before s terminates.

The *next* operation can also used for communication. For instance, in the piece

of code we just saw,  $recv\ a$  can be replaced by  $next\ a$ , and b=5;  $send\ b$ ;, can be replaced by  $next\ b=5$ . In other words, next behaves like a send if it appears on the left side of an assignment, and like recv otherwise.

Only the procedure that takes a channel by reference may send on that channel. A channel may be passed by reference to at most one of the procedures. E.g.,

```

int f(chan int &x, chan int y) { x++; y--; }

int g(chan int z) { z--; }

void main() {

chan int a; a=0; chan int b; b=1;

f(a, b); par f(b, a); par g(a); // OK: a=1, b=2

}

```

In the above piece of code, executes f(a,b) in parallel with f(b,a), and both run in parallel with g(a); The first f takes a by reference and a is incremented once, while the second f takes b by reference and increments b by 1. g does not take any variable by reference. Therefore, it does not affect the values of a and b. So, the values of a and b become 1 and 2 respectively after the execution of the second line in main.

The following line would be illegal in main.

f(a, a); par f(a, b); // incorrect: a is passed twice by reference — compiler reject Due to this restriction (enforced at compile time), concurrently running procedures never share memory — every task maintains its own local copy. The sender task alone references the actual copy, and there can be only one sender task on a channel.

In general, if there are two sender tasks on a particular channel in the code section of the program, then the compiler rejects the program to guarantee determinism. Summarily, the asynchronous parts in SHIM are totally independent because they never share memory. Sharing is only through explicit synchronization using rendezvous communication. This makes SHIM deterministic.

It is not necessary for the statements in the *par* statement to be procedure calls. For instance:

```

b = 10

send b; // Send 10 on b (wait for task 1)

// now b = 10

}

}

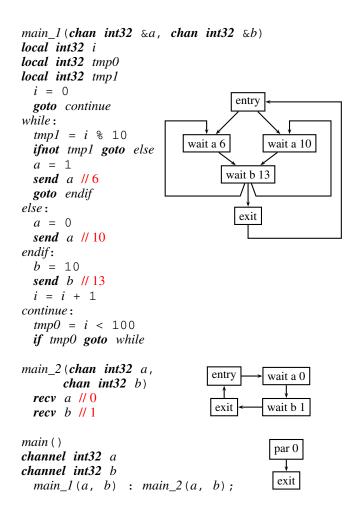

The SHIM compiler dismantles the above code as:

/* Task 1 */

void main1 (int &a, int b) {

a = 5;

send a; // Send 5 on a (wait for task 2)

// now a = 5

recv b; // Receive b (wait for task 2)

// now b = 10

/* Task 2 */

void main2 (int a, int &b) {

recv a; // Receive a (wait for task 1)

// now a = 5

b = 10

send b; // Send 10 on b (wait for task 1)

// now b = 10

}

void main()

chan int a, b;

main1(a,b); par main2(a,b);

/* a = 5, b = 10 */

```

Task 1 (represented by *main*1), being the sender on *a*, takes *a* by reference. Similarly, *main*2 takes *b* by reference. The two peer tasks communicate on channels *a* and *b*. Tasks 1 and 2 are executed in parallel. The *send a* in task 1 waits for task 2 to receive the value. The tasks therefore rendezvous, then continue to run after the communication takes place. Next, the two tasks rendezvous at *b*. This time, task 2 sends and task 1 receives.

Here is another example that illustrates how the *send* and *recv* instructions enable communication between concurrently running procedures.

```

void f(chan int &x) { /* reference to a */

x = 3; /* modifies a, a is 3 */

send x; /* sends 3 */

x = 4; /* modifies a, a is 4 */

}

void g(chan int y, chan int &z) {

y = 5; /* modifies local copy */

recv y; /* receives 3, y is 3 */

z = y; /* modifies b */

}

```

```

void main() {

chan int a; a=0; chan int b; b=1;

f(a); par g(a, b); // a=4, b=3

}

```

Here, send x in f and recv y in g synchronize and the value of x in f is copied into y in g. Variables x and y are paired in this communication because both are instances of variable a from main, that is, x is a reference to a and y is a "by-value" reference to a. We say that procedures f and g share variable a from main even if only f has access to the value of variable a through x.

When two or more concurrent procedures share the same variable a in this sense, all of them must participate in each communication on a. Hence, each procedure reaching a *send* x or *recv* y instruction (where x resp. y is the name of the local instance of a) blocks, that is, stops executing until every procedure involved is blocked on a. Then, a communication takes place atomically.

In other words, the primitive communication mechanism in SHIM is the multiway rendezvous that requires all participants in a communication to synchronize – there can be multiple receivers but only one sender on a channel. Of course, other traditional communication mechanisms can be built using this multiway rendezvous. For instance, the fifo procedure described later in this section implements buffered channels.

In SHIM, there are rules for the (static) disambiguation of multiple-sender-multiple-receiver communications. In particular, a procedure can only send values on a pass-by-reference parameter channel. For instance,

```

void snd (chan int \&x) { send x; } void rcv (chan int y) { recv y; } void main () { chan int a; a=0; snd (a); } // OK void main () { chan int a; a=0; snd (a); par rcv (a); par rcv (a); } // OK void main () { chan int a; a=0; snd (a); par snd (a); } // incorrect void main () { chan int a; a=0; rcv (a); } // OK — receives 0 (the last value on the channel) void main () { chan int a; a=0; rcv (a); par rcv (a); } // OK — both receive 0 In the absence of a sender, the rendezvous deadlocks. Competing synchronization barriers may also cause deadlocks. For example, void f (chan int \&x, chan int \&y) { send x; send y; } void g (chan int x, chan int y) { recv x; recv y; } void main () { chan int a; a=0; chan int b; b=0; f (a, b); par g (b, a); } // deadlocks

```

Procedures f and g share a and b from main; f is waiting to synchronize on a whereas g is blocked on b. Therefore, neither synchronization attempt completes.

This means coding in SHIM involves tracking down deadlocks, but we prefer reproducible fatal errors to hard-to-detect, hard-to-reproduce data races. Deadlock detection techniques are discussed in the later chapters.

A terminated procedure is no longer compelled to rendezvous. E.g.,

```

void f(chan int &x, chan int &y) { send x; send y; send x; }

void g(chan int x) { recv x; }

void main() {

chan int a; a=0; chan int b; b=0;

f(a, b); par g(b); // no deadlock: a is only shared by f

f(a, b); par g(a); // no deadlock: a is only shared by f once g returns

}

```

This is one of the two reasons multiway rendezvous is fundamental to SHIM. Because procedures may terminate, a multiway channel may dynamically shrink; because concurrent procedures may further divide into more concurrent procedures, a multiway channel may dynamically extend. A procedure (or a task) that takes a channel by value, may pass the channel to its subprocedures (or subtasks) only by value.

Summarily, a *send* x or a *recv* x waits for all tasks that access channel x, to either communicate on x or terminate. Once this condition is satisfied, the value is copied from sender to all receivers. If there is no sender at the rendezvous, the last value written on the channel is copied to the receivers. After this, the tasks continue execution independently. When a task executes a statement x = a, it writes a to its local copy of x if the task is a receiver. The sender alone writes to the actual location of x.

To perform I/O in SHIM, we declare *cin* and *cout* as channels. All tasks that take *cin* by value, can read the input. The task that takes *cout* by reference, can write to the output. To do this, we allow the *main* function to take parameters. *main* takes *cin* by value and *cout* by reference. A "hello world" program in SHIM will look like this:

```

void main(chan char cin, chan char &cout) {

cout << 'H';

cout << 'e';

cout << 'l';

..

cout << 'l';

cout << 'l';

}</pre>

```

The SHIM scheduler is a part of the runtime environment of the SHIM target program. It runs the asynchronous (communication-free) parts of the program independently — allowing the environment (operating system, hardware, etc.) to schedule these asynchronous sections of tasks with arbitrary interleavings. However, the SHIM scheduler will not violate the interthread communication rules forcing communication actions to synchronize.

All legal SHIM programs must be provably scheduling independent. For example, the *cell* function below implements a one-place buffer with an infinite loop that

alternatively reads from its input channel and writes to its output channel. Then, by combining recursion and parallel composition, the fifo function chains n one-place buffers to build a fifo of size n.

```

void cell(chan int i, chan int &o) {

while (true) { recv i; o = i; send o; }

}

void fifo(chan int i, chan int &o, int n) {

chan int c; chan int m; m = n - 1;

if (m>0) { cell(i, c); par fifo(c, o, m); }

else { cell(i, o); }

}

```

The distribution of data tokens in the fifo is under the control of the scheduler. For instance, one scheduling policy may chose to move data tokens toward the output of the fifo eagerly; another may move data tokens lazily. Nevertheless, because this is a legal SHIM program, we know that the output of the fifo will always be the same for a particular input sequence.

SHIM also has an exception mechanism that is layered on top of its communication mechanism to preserve determinism.

```

void source (chan int &a) throws T {

while (a > 0) {

a = a - 1;

send a;

}

throw T;

}

void sink (chan int b) {

while (1)

recv b;

}

void main() {

chan int x = 5;

try {

source(x); par sink(x);

} catch (T) {}

}

```

The *source* procedure in the above piece of code sends 4, 3, 2, 1, and 0 to the *sink*. The *sink* procedure calls *recv* five times to synchronize with the *source*'s sends. Then, *source* throws an exception *T*. When *sink* tries to receive the sixth time, it is poisoned by the *source* and terminated. It should be noted that the *sink* receives the poison only when it tries to communicate with *source*. As described, exceptions are propagated to other tasks only during communication, making the exception model of SHIM deterministic. We discuss a few more examples of SHIM programs with exceptions in the following chapters.

The central hypothesis of SHIM is that its simple, deterministic semantics

helps both programming and automated program analysis. That we have been able to devise truly effective mechanisms for clever code generation and analysis (e.g., deadlock detection) that can gain deep insight into the behavior of programs, vindicates this view. The bottom line: if a programming language does not have simple semantics, it is really hard to analyze its programs quickly or precisely.

In the following chapters, we describe a series of code generation techniques suitable for parallel processors. Each actually works on a slightly different dialect of the SHIM language, although all use the Kahn-with-rendezvous communication scheme. The reason for this diversity is historical; we added features to the SHIM model as we discovered the need for them. Our benchmarks are all batch programs; we do not yet deal with reactive systems.

# Chapter 4

# Compiling SHIM to a Shared Memory Architecture

We have described the SHIM programming language in the previous chapter. To prove that the language can be practical, we describe a compiler that generates C code and calls the *Pthread* library for parallelism.

As discussed in the previous chapter, the SHIM language [47; 116] only allows deterministic message-passing communication to guarantee race freedom. The programming model allows SHIM compilers to use a simple syntactic check to verify that runtime scheduling choices cannot change a program's IO behavior. While this model does restrict how concurrent tasks may interact, the burden for the programmer and the performance penalty are a small price for correctness.

In this chapter, we demonstrate how SHIM facilitates writing interesting, time efficient parallel programs for shared-memory multiprocessors. The challenge is minimizing overhead - implementing SHIM's multiway rendezvous communication with exceptions efficiently is the main code generation challenge. Each communication action acquires the lock on a channel, checks whether every connected process had also blocked (whether the rendezvous could occur), and then checks if the channel is connected to a poisoned process (an exception had been thrown).

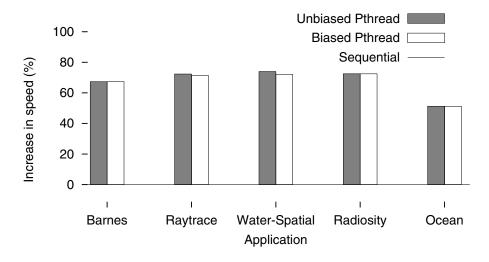

We implement a parallel JPEG decoder and an FFT to show how SHIM helps with coding and testing different schedules during design exploration (Section 4.2). We present a compiler that generates C code that calls the POSIX thread ("Pthread") library for shared-memory multiprocessors (Section 4.3). For the JPEG and FFT examples, our compiler's output achieves 3.05 and  $3.3 \times$  speedups on a four-core processor (Section 4.4).

```

void h (chan int &A) {

A = 4; send A;

void g(chan int A) {

A = 2; send A;

recv A;

recv A;

void j(chan int A) throws Done {

recv A;

void main() {

throw Done;

try {

chan int A;

f(A); par g(A);

void f(chan int &A) throws Done {

} catch (Done) {}

h(A); par j(A);

```

Figure 4.1: A concurrent SHIM program with communication and exceptions

## 4.1 Reviewing SHIM

SHIM [116] is a concurrent programming language designed to guarantee scheduling independence. The input-output function of a SHIM program does not depend on scheduling choices; that is, if two concurrent tasks are ready to run, choosing which to run first does not affect the program's function.

It adopts an asynchronous concurrency model, à la Kahn networks [70] (SHIM tasks can only block on a single channel), that uses CSP-like rendezvous [61]. The language does not expose shared memory to the programmer, but it does provide single-sender multiple-receiver synchronous communication channels and asynchronous exceptions. Both mechanisms were designed to prevent scheduling decisions from affecting function.

SHIM's syntax is a C subset augmented with constructs for concurrency, communication, and exceptions. It has functions with by-value and by-reference arguments, but no global variables, pointers, or recursive types.

The par construct starts concurrent tasks. p par q starts statements p and q in parallel, waits for both to complete, then runs the next statement in sequence.

To prevent data races, SHIM forbids a variable to be passed by reference to two concurrent tasks. For example,

```

void f(int &x) {} void g(int x) {}

void main() {

int x, y;

f(x); par g(x); par f(y);

f(x); par f(x);

// OK

// rejected because x is passed by reference twice

}

```

Internally, our compiler only supports parallel function calls. If p in p par q is

not a function call, *p* is transformed into a function whose interface—the formal arguments and whether they are by-reference or by-value—is inferred [116].

SHIM's channels enable concurrent tasks to synchronize and communicate without races. The *main* function in Figure 4.1 declares the integer channel A and passes it to f and g, then f passes it to h and g. Tasks f and g send data with *send* g. Tasks g and g receive it with g receive g receive it with g receive g rece

A channel resembles a local variable. Passing a channel by value copies its value, which can be modified independently. A channel must be passed by reference to senders.

Communication is blocking: a task that attempts to communicate must wait for all other connected tasks to engage in the communication. If the synchronization completes, the sender's value is broadcast to the receivers. In Figure 4.1, 4 is broadcast from h to g and j. Task g blocks on the second send A because task j does not run a matching recv A.

Like most formalisms with blocking communication, SHIM programs may deadlock. But deadlocks are easier to fix in SHIM because they are deterministic: on the same input, a SHIM program will either always or never deadlock.

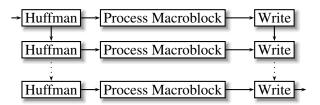

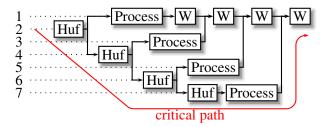

Figure 4.2: Dependencies in JPEG decoding

Figure 4.3: Seven-task schedule for JPEG

SHIM's exceptions enable a task to gracefully interrupt its concurrently running siblings. A sibling is "poisoned" by an exception when it attempts to communicate with a task that raised an exception or with a poisoned task. For example, when *j*

in Figure 4.1 throws *Done*, it interrupts *h*'s blocked *send A* and *g*'s blocked *recv A*. An exception handler runs after all the tasks in its scope have terminated or been poisoned.

### 4.2 Design exploration with SHIM

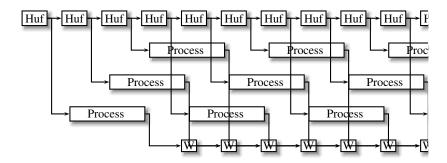

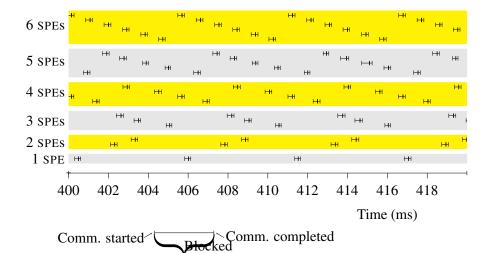

SHIM facilitates the coding and testing of different schedules—a key aspect of design exploration for parallel systems. To illustrate, we describe implementing two parallel algorithms in SHIM: a JPEG decoder and an FFT.

#### 4.2.1 Porting and parallelizing a JPEG decoder