## CardCounter

Final Project Report

Team Members: Christos Savvopoulos Hugh Gordon Nathan Rogan

## Table of Contents

#### 1. Introduction

## 2. Project Design

- i. Design

- ii. Components

- iii. Software

## 3. Implementation Issues

- i. Hardware & Interfacing

- ii. Lighting

- iii. Physical

## 4. Lessons and Work Done

- i. Chris

- ii. Nate

- iii. Hugh

#### 5. Code

- i. C code

- ii. lab5 (top-level entity)

- iii. histo (histogram counter)

- iv. communication

- v. CCD\_Capture (edited)

## 1. Introduction

We have written a playing card recognition system using the CCD camera provided with the DE2 board. Using camera input and specialized histogramming techniques, our project detects the value and suite of a given playing card. Given 10 minutes of training, our system will work with a large variety of different playing cards.

The image data comes from the CCD camera into the DE2 board as a stream of pixels. As each pixel is received, its color is determined using a set of hard coded thresholds. Each time a pixel of a given color arrives, a register corresponding to that color is incremented. Once the entire picture is received, the software can use the collected data to determine how many pixels of each color are in the picture.

Each playing card has a unique number of colored pixels on it. The software program that we wrote on top of the NIOS processor uses this data to determine which card has been placed. While this method is not 100% effective, mainly due to noisy data from the CCD camera, using range and averaging techniques has allowed us to achieve very high rates of accuracy in card recognition.

It is worth noting that throughout the development process we implemented unsuccessfully various solutions to solve different issues that had arisen. Some of these failed solutions and the reasoning behind there implementation as well as their failure are included in Appendix A.

# 2. Project Design& System Architecture

#### i. Design

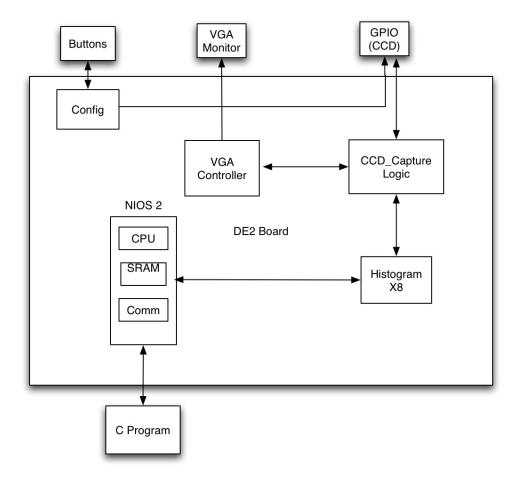

When we set off to design this system we had two goals in mind: recognizing cards by counting pixels and separating the tasks better suited to software or hardware. Some parts of the design are inherently hardware, such as the CCD Capture logic and the VGA output. Other tasks, such as an algorithm that recognizes cards are clearly better done in software. To count the number of pixels of a certain color, there are multiple approaches. In the end, we decided to implement the system such that as the CCD\_Capture unit reads the data, they are counted by multiple histogram components. When a new frame arrives, the counter is stored in a register.

On the software side of things, we want to know the number of pixels for each color. The communication between the two worlds happens through the Avalon bus. In addition to that, to make the system more flexible we decided to give the program the power to define the color of each counter on the fly. This is done specifying a minimum and maximum red, green, and blue component.

Not only did this save a huge amount of compiling time (since software compiles a lot faster than hardware) but it also made the system a lot more expandable, since different algorithms could try to change the thresholds on the fly.

## ii. Components

#### CCD\_Capture:

Reads from the CCD Camera, and outputs the data component of the currently read pixel.

Clock speed: 25 MHZ Input: Clock, GPIO\_1

Output: data (10 bits), new frame flag, new pixel flag

#### RAW2RGB:

The CCD is a 2D Array of *either* red, green, or blue sensors. This component does some basic image processing (averaging pixels) and gives out the red, green and blue components for each pixel.

Input: pixel clock, data (10 bits), X & Y position

Output: red, green, blue (10 bits each)

#### Histogram:

This histogram logic takes in the stream of RGB data from the camera logic. Each module (there are 8) is configurable from the software to count up pixels that match a given set of tolerances placed on the red, green and blue values. For instance, to match red, one could set the R tolerance to be between 700 and 1023 and the G and B tolerances to be from 0 to 300. The suitability of these values is highly dependent on the environment.

Input: min and max threshold (32 bits each)

Output: Count (32 bit wide) of how many pixels fit the RGB constraints

#### VGA Controller:

The VGA controller takes the data from the camera logic and turns it into a VGA signal so that it can be displayed on a normal computer monitor.

Input: r, g, b: 10bits each Output: VGA signals

#### Config and Buttons:

The buttons were configured as input to control the settings on the camera. We needed a way to adjust the exposure and turn the camera on and off. The buttons on the DE2 board provided a simple solution.

#### NIOS 2e:

The standard processor used with the DE2 board. The edition we used had a 50MHZ clock, 524K of onboard SRAM and used the JTAG UART system to communicate with the terminal.

#### Communication:

This component, as the name suggests, was responsible for communicating data between the hardware part and the software part of our solution. It uses the Avalon bus to perform 32 bit reads (accum) and writes (min, max) from/to the hardware.

```

Input: 8 x accum (32 bits each)

Output: 8 x min, max (32 bits each)

```

#### iii. Software

Aside from counting the pixels of various colors, this is where all the image processing got accomplished. The software program has two modes of operation. The first mode is the learning mode. In this mode, the user is asked to place cards down and type in their values (i.e. king of spades or 2 of clubs). The software then records range of values that are read for number of red and black pixels over a large number of frames. These two ranges (one for red and one for black) are unique for each card. Once the ranges are paired with a given card, that card can be recognized. The second mode of operation is the reorganization mode. In this mode, the software accesses its previously learned data and attempts to match a given card to it. In this case, instead of taking the range of values over a large number of frames, it takes the average of these values and looks to see weather or not this average fits inside each given remembered range. If it does, the corresponding card value is printed out, otherwise, it tries again. Pseudo code is provided below.

## pseudocode

```

setThresholds();

//Learning phase

while(1) {

read card number and suit from user

if user enters 0 as number, proceed to next phase

take 2000 readings from camera

store the minimum and maximum results for each color, under the

card index

}

//Recognizing phase

```

```

while(1) {

take 1000 readings and average the results for each color

for each card X that we learned in the previous phase

if the averages are within the ranges of X

keep the card that is the best fit*

print that card

}

```

\*falls most closely in the centre of the range

## 3. Implementation Issues

## i. Hardware & Interfacing

During the proposal period, we decided to break the project into three separate pieces: interfacing with camera, hardware processing and software. We assumed that interfacing with the software would be simple, as we had already done that previously.

This approach worked, until we tried to combine software and hardware. With the timing differences between the camera logic and the processor, the software would not upload on the DE2 board. The camera module runs at 25MHz. In addition to that, an inverted version of that clock is also used that can optionally have an offset. The processor, as well as the rest of the system, runs at 50MHz.

The problem being that we could not upload the software, we tried many different approaches. First, we tried to follow the lab3 tutorial over and over again, making sure we added every NIOS\_System component correctly. The next approach was to strip down the system, component by component so as to find the cause of the trouble. Though, we were able to confine the problem within ~30 lines of code, we were not able to resolve the problem. Having tracked down the problem, we experimented with re-writing the obtained code to VHDL, and thalso with generating the NIOS System in Verilog.

Our next approach was to research how the NIOS system works and try to track down online discussions from people who had the same issues. The consensus seemed to be the reason we mention above, namely the timing differences. A careful review of the info/warnings produced by Quartus confirmed this.

The multiple clocks in a single module solution could have been solved in two ways. Add a method to align clock skew consistently over the module or to remove the component from the NIOS system and connect the two in the top level component. We chose the latter.

## ii. Lighting

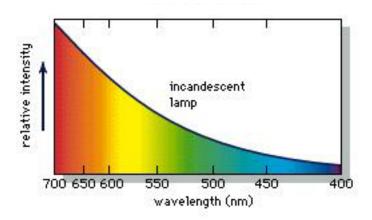

With any form of computer vision, obtaining good lighting conditions is paramount. In this project, it was especially important that we had reproducible and optimal lighting conditions. To this end, we researched and tested numerous different lighting choices to find one that would work optimally for us. A central concern was whether to use incandescent light or fluorescent light. Through our research, we learned that the issue at hand was obtaining a proper white balance for our CCD camera. We learned that incandescent light has a waveform that would offset our image in a negative way:

From <a href="http://users.mis.net/~pthrush/lighting/glow.html">http://users.mis.net/~pthrush/lighting/glow.html</a>

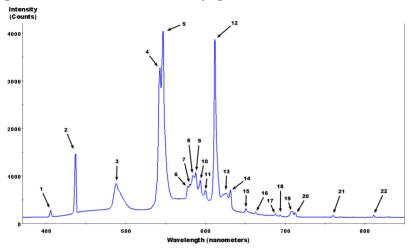

As one can see from the above diagram, incandescent light has a lot of red in it. This red interfered significantly with our ability to detect red in cards. Fluorescent lamps however proved to be much more evenly spread:

From <a href="http://en.wikipedia.org/wiki/Image:Fluorescent">http://en.wikipedia.org/wiki/Image:Fluorescent</a> lighting spectrum peaks labelled.gif

The above spectra is from a typical fluorescent lamp, as can be seen, the peaks are much more in the green and blue regions, which could easily ignore. We also realized that multiple light sources were significantly better than one as many light sources delivered much more uniform light to the face of the card. Having uniform light hitting the card is very important. It means that moving the card does not affect the intensity perceived by the camera.

## iii. Physical

Similar to lighting, we had a lot of physical issues with this project. It turned out that the placement of the camera, and the isolation of the camera-card system was highly important. Again, we did significant testing in this area, trying everything from a wood

box with a green felt bottom to a cardboard box lit with Christmas lights to an opaque cake cover with a hole in the top for the camera.

## 4. Lessons Learned

#### i. Chris

#### Contribution:

- Designed the system and the specifics of the hardware architecture.

- Developed camera and communication logic that ultimately allowed for successful use of the Avalon bus.

- Developed C interface.

**Lesson:** This project taught me the importance of being patient with other team members. There were some times when I thought that the voiced ideas were wrong, but upon further consideration proved insightful. Also, when comparing this experience with the PLT project, I can understand how important it is to appoint a team leader. Finally, I wish we had researched the workings of NIOS more systematically. We could have avoided a lot of time-consuming experimentation if we had done so.

## ii. Hugh

#### Contribution:

- Helped with VHDL.

- Built a stabilized box which allowed for optimal data acquisition.

**Lesson:** Doing something this low level in system design was a real eye opener. Besides sharpening my VHDL skills and broadening my understanding of digital systems, I was shown the importance of good communication and planning amongst team members. We could have planned and shared out the project much more effectively. We were sometimes working on the same thing. Good planning and communication could have made us much more effective as a working unit. Finally, I learned that the lower level you are, the more time you need to leave for debugging. Debugging this took orders of magnitude more time than my most complex operating systems endeavors.

#### iii. Nate

#### Contribution:

- Tested various algorithms for suitability.

- Extensively researched cause of failure with the Avalon and tried different hardware configurations.

- Developed C program.

**Lesson:** The main thing I learned in this project was that a clear review of a system on paper is worth days in development time. The ability to understand the tools design

implementation from the top level allows for a cleaner solution and a less buggy implementation. While I did take a systematic debugging approach when our system was show to have a critical flaw I did not have enough sense to stop and reanalyze the system. Working with team members gave a fresh review of the system and eventually led to the solution from Chris. There were some fun times when things went well. There were other times when the tension was so thick it was palpable. A calm demeanor and patience as hard as it was to obtain at those times led to a better working environment.

## 5. Code

The code for the following components follows in the order shown below. They were printed to .pdf from the editors of these files, and then appended to the final pdf (for highlighting).

- i. C code

- ii. lab5 (top-level entity)

- iii. histo (histogram counter)

- iv. communication

- v. CCD\_Capture (edited)

Edited: new frame flag, used by the accumulators.

```

* "Hello World" example.

* This example prints 'Hello from Nios II' to the STDOUT stream. It runs on

* the Nios II 'standard', 'full featured', 'fast', and 'low cost' example

* designs. It runs with or without the MicroC/OS-II RTOS and requires a STDOUT

* device in your system's hardware.

* The memory footprint of this hosted application is ~69 kbytes by default

* using the standard reference design.

* For a reduced footprint version of this template, and an explanation of how

* to reduce the memory footprint for a given application, see the

* "small_hello_world" template.

* /

#include <io.h>

#include <system.h>

#include <stdio.h>

typedef unsigned int uint;

#define N 2

uint pack(uint red, uint green, uint blue) {

return ((red&0x3FF)<<20)

((green&0x3FF)<<10)

((blue&0x3FF));

}

void put(int n, int minR, int minG, int minB, int maxR, int maxG, int maxB) {

pack(minR, minG, minB));

IOWR_32DIRECT(COMMUNICATION_0_BASE, 4*n*2,

IOWR_32DIRECT(COMMUNICATION_0_BASE, 4*(n*2+1), pack(maxR, maxG, maxB));

}

uint get(int n) {

return IORD_32DIRECT(COMMUNICATION_0_BASE, 4*n);

struct range {

uint min, max;

};

struct range db[15][4][2]; // { spades, clubs, hearts, diamonds } * 14 cards * {redRange,

blackRange }

int vv[15][4];

int cardIndex(char c) {

switch(c) {

case 's': case 'S': return 0;

case 'c': case 'C': return 1;

case 'h': case 'H': return 2;

case 'd': case 'D': return 3;

default: return -1;

const char cardLookup[4] = { 'S', 'C', 'H', 'D' };

uint min(uint a, uint b) {

if(a<b)

return a;

else

return b;

}

```

```

uint max(uint a, uint b) {

if(a>b)

return a;

else

return b;

}

uint sqClamp(uint a) {

if(a>=1000)

return 1000*1000;

else

return a*a;

}

void multiGet(struct range col[8], int n) {

int val,i,j;

for(i=0;i<8;i++) {</pre>

col[i].min=0xfffffff;

col[i].max=0;

}

//printf("Reading");

for(i=0; i<1000;i++) {</pre>

usleep(5000);

for(j=0;j<8;j++) {

val=get(j);

col[j].min=min(val,col[j].min);

col[j].max=max(val,col[j].max);

//printf(" Done!\n");

}

void waitStable() {

struct range col[8];

int i;

while(1) {

multiGet(col,300);

for(i=0;i<8;i++)</pre>

if(col[i].max-col[i].min > 1000)

return;

}

int main()

int n,s,i,j;

uint red, black;

char c;

struct range col[8];

memset(vv,0,sizeof(int)*15*4);

put(0, 700,0,0, 1023,300,300);

put(1, 0,0,0, 300,300,300);

while(1) {

```

```

printf("Please enter card number (1-14) followed by [s]pade, [c]lub, [h]eart,

[d]iamond, and press enter to 'teach' that card: ");

scanf("%i%c",&n,&c);

s=cardIndex(c);

if(n==0)

break;

printf("Reading... ");

multiGet(col,1000);

printf("Done!\n");

db[n][s][0]=col[0];

db[n][s][1]=col[1];

vv[n][s]=1;

db[n][s][0].min*=0.96; db[n][s][0].max*=1.04;

db[n][s][1].min*=0.96; db[n][s][1].max*=1.04;

[1].min,db[n][s][1].max);

while(1) {

waitStable();

printf("Recognizing... ");

const int samples = 1000;

uint i,red=0,black=0;

for(i=0; i<samples; i++) {</pre>

usleep(5000);

red+=get(0);

black+=get(1);

red/=samples;

black/=samples;

//printf("Red=%u Black=%u\n",red,black);

uint closest=0xfffffff;

uint closeN=0, closeS=0;

for(i=1;i<=14;i++) {

for(j=0;j<4;j++) {</pre>

if(!vv[i][j])

continue;

if(db[i][j][0].min <= red && red <= db[i][j][0].max &&</pre>

db[i][j][1].min <= black && black <= db[i][j][1].max) {

uint redAvg = (db[i][j][0].min+db[i][j][0].max)/2;

uint blackAvg=(db[i][j][1].min+db[i][j][1].max)/2;

if( sqClamp(red-redAvg)+sqClamp(black-blackAvg) < closest) {</pre>

closest=sqClamp(red-redAvg)+sqClamp(black-blackAvg);

closeN=i; closeS=j;

}

}

if(closeN)

printf("%u %c\n", closeN, cardLookup[closeS]);

}

return 0;

}

```

```

1 library IEEE;

2 use IEEE.std_logic_1164.all;

3 use IEEE.std logic arith.all;

4 use IEEE.std logic unsigned.all;

6 entity lab5 is

port (

9

signal CLOCK_50 : in std_logic;

-- 50 MHz clock

SRAM_DQ : inout std_logic_vector(15 downto 0); -- Data bus 16 Bits

12

SRAM_ADDR : out std_logic_vector(17 downto 0); -- Address bus 18 Bi

ts

SRAM_UB_N,

-- High-byte Data Ma

sk

14

SRAM LB N,

-- Low-byte Data Mas

k

SRAM WE N,

-- Write Enable

SRAM CE N,

-- Chip Enable

SRAM_OE_N : out std_logic;

-- Output Enable

KEY : in std_logic_vector(3 downto 0);

-- Push buttons

SW : in std_logic_vector(17 downto 0);

-- DPDT switches

21

HEX0, HEX1, HEX2, HEX3, HEX4, HEX5, HEX6, HEX7 -- 7-segment display

: out std_logic_vector(6 downto 0);

LEDG : out std_logic_vector(8 downto 0);

-- Green LEDs

24

25

LEDR : out std_logic_vector(17 downto 0);

-- Red LEDs

GPIO_1 : inout std_logic_vector(35 downto 0);

27

-- SDRAM

DRAM_DQ : inout std_logic_vector(15 downto 0); -- Data Bus

DRAM_ADDR : out std_logic_vector(11 downto 0); -- Address Bus

-- Low-byte Data Mas

DRAM LDQM,

k

32

DRAM_UDQM,

-- High-byte Data Ma

DRAM_WE_N,

-- Write Enable

-- Column Address St

34

DRAM_CAS_N,

robe

DRAM_RAS_N,

-- Row Address Strob

DRAM_CS_N,

-- Chip Select

-- Bank Address 0

DRAM_BA_0,

-- Bank Address 0

DRAM_BA_1,

DRAM CLK,

-- Clock

-- Clock Enable

DRAM_CKE : out std_logic;

41

42

-- VGA output

43

VGA_CLK,

-- Clock

44

VGA_HS,

-- H_SYNC

45

VGA_VS,

-- V_SYNC

VGA BLANK,

-- BLANK

47

VGA_SYNC : out std_logic;

-- SYNC

VGA R,

-- Red[9:0]

49

-- Green[9:0]

VGA_G,

```

```

VGA_B : out std_logic_vector(9 downto 0)

-- Blue[9:0]

);

54 end lab5;

56 architecture rtl of lab5 is

component nios_system is

port (

-- 1) global signals:

signal clk : IN STD LOGIC;

signal reset_n : IN STD_LOGIC;

-- the communication 0

signal Count0_to_the_communication_0 : IN STD_LOGIC_VE

CTOR (31 DOWNTO 0);

signal Count1_to_the_communication_0 : IN STD_LOGIC_VE

CTOR (31 DOWNTO 0);

signal Count2_to_the_communication_0 : IN STD_LOGIC_VE

CTOR (31 DOWNTO 0);

signal Count3_to_the_communication_0 : IN STD_LOGIC_VE

CTOR (31 DOWNTO 0);

signal Count4_to_the_communication_0 : IN STD_LOGIC_VE

CTOR (31 DOWNTO 0);

signal Count5_to_the_communication_0 : IN STD_LOGIC_VE

CTOR (31 DOWNTO 0);

signal Count6_to_the_communication_0 : IN STD_LOGIC_VE

CTOR (31 DOWNTO 0);

signal Count7_to_the_communication_0 : IN STD_LOGIC_VE

CTOR (31 DOWNTO 0);

signal max0_from_the_communication_0 : OUT STD_LOGIC_V

ECTOR (31 DOWNTO 0);

signal max1_from_the_communication_0 : OUT STD_LOGIC_V

ECTOR (31 DOWNTO 0);

signal max2_from_the_communication_0 : OUT STD_LOGIC_V

ECTOR (31 DOWNTO 0);

signal max3_from_the_communication_0 : OUT STD_LOGIC_V

ECTOR (31 DOWNTO 0);

signal max4_from_the_communication_0 : OUT STD_LOGIC_V

ECTOR (31 DOWNTO 0);

signal max5_from_the_communication_0 : OUT STD_LOGIC_V

ECTOR (31 DOWNTO 0);

signal max6_from_the_communication_0 : OUT STD_LOGIC_V

ECTOR (31 DOWNTO 0);

signal max7_from_the_communication_0 : OUT STD_LOGIC_V

ECTOR (31 DOWNTO 0);

signal min0 from the communication 0 : OUT STD LOGIC V

ECTOR (31 DOWNTO 0);

signal min1 from the communication 0 : OUT STD LOGIC V

ECTOR (31 DOWNTO 0);

signal min2_from_the_communication_0 : OUT STD_LOGIC_V

ECTOR (31 DOWNTO 0);

signal min3_from_the_communication_0 : OUT STD_LOGIC_V

ECTOR (31 DOWNTO 0);

signal min4_from_the_communication_0 : OUT STD_LOGIC_V

ECTOR (31 DOWNTO 0);

signal min5_from_the_communication_0 : OUT STD_LOGIC_V

```

```

ECTOR (31 DOWNTO 0);

signal min6_from_the_communication_0 : OUT STD_LOGIC_V

ECTOR (31 DOWNTO 0);

signal min7 from the communication 0 : OUT STD LOGIC V

ECTOR (31 DOWNTO 0);

-- the_sram

signal SRAM_ADDR_from_the_sram : OUT STD_LOGIC_VECTOR

(17 DOWNTO 0);

signal SRAM CE N from the sram : OUT STD LOGIC;

signal SRAM_DQ_to_and_from_the_sram : INOUT STD_LOGIC_

VECTOR (15 DOWNTO 0);

signal SRAM_LB_N_from_the_sram : OUT STD_LOGIC;

signal SRAM_OE_N_from_the_sram : OUT STD_LOGIC;

94

signal SRAM_UB_N_from_the_sram : OUT STD_LOGIC;

signal SRAM WE N from the sram : OUT STD LOGIC

);

end component;

100 component histo is port (

: in std_logic; --50MHz

clk

102

: in std logic vector(9 downto 0);

R

: in std_logic_vector(9 downto 0);

G

104

: in std_logic_vector(9 downto 0);

: in

std_logic;

new_pixel

: in

new_frame

std_logic;

: in std_logic_vector(31 downto 0);

Min

: in std_logic_vector(31 downto 0);

Max

: out std_logic_vector(31 downto 0) );

count

110 end component;

112 component VGA_Controller is port (

signal iRed : in std_logic_vector(9 downto 0);

114

signal iGreen : in std_logic_vector(9 downto 0);

signal iBlue : in std_logic_vector(9 downto 0);

116

signal oRequest : out std logic;

-- signal VGA Side

signal oVGA_R : out std_logic_vector(9 downto 0);

118

signal oVGA_G : out std_logic_vector(9 downto 0);

119

signal oVGA_B : out std_logic_vector(9 downto 0);

signal oVGA_H_SYNC : out std_logic;

signal oVGA_V_SYNC : out std_logic;

signal oVGA_SYNC : out std_logic;

signal oVGA_BLANK : out std_logic;

124

signal oVGA_CLOCK : out std_logic;

-- Control Signal

signal iCLK : in std logic;

signal iRST N : in std logic );

129 end component;

131 component Reset_Delay is port (

signal iCLK : in std_logic;

signal iRST

: in std_logic;

134

signal oRST_0: out std_logic;

signal oRST_1: out std_logic;

signal oRST_2: out std_logic );

137 end component;

```

```

139 component CCD_Capture is port (

signal oDATA : out std_logic_vector( 9 downto 0);

signal oDVAL : out std_logic;

142 signal oX_Cont : out std_logic_vector(10 downto 0);

143 signal oY_Cont : out std_logic_vector(10 downto 0);

144 signal oFrame_Cont : out std_logic_vector(31 downto 0);

145 signal oNewFrame : out std_logic;

146 signal iDATA : in std_logic_vector(9 downto 0);

147 signal iFVAL : in std_logic;

148 signal iLVAL : in std_logic;

149 signal iSTART : in std_logic;

150 signal iFND : in std_logic;

: out std logic;

signal oDVAL

signal iEND

: in std logic;

signal iCLK

: in std logic;

signal iRST

: in std_logic );

153 end component;

154

155 component RAW2RGB is port (

signal oRed

: out std_logic_vector( 9 downto 0);

signal oGreen : out std_logic_vector( 9 downto 0);

signal oBlue : out std_logic_vector( 9 downto 0);

signal oDVAL

: out std_logic;

signal iX_Cont : in std_logic_vector(10 downto 0);

signal iY_Cont : in std_logic_vector(10 downto 0);

: in std_logic_vector( 9 downto 0);

signal iDATA

: in std_logic;

signal iDVAL

signal iCLK : in sta_rogre.

signal iRST : in std_logic );

164

signal iRST

166 end component;

168 component Sdram_Control_4Port is port (

169 -- HOST Side

signal REF_CLK

: in std_logic;

: in std_logic;

signal RESET_N

172

-- FIFO Write Side 1

174

176

signal WR1_LOAD

178

179

signal WR1 FULL

-- FIFO Write Side 2

184

signal WR2 USE

: out std_logic_vector( 8 downto 0);

-- FIFO Read Side 1

signal RD1 DATA

: out std_logic_vector(15 downto 0);

194

signal RD1

: in std_logic;

```

```

signal RD1_ADDR : in std_logic_vector(23 downto 0);

signal RD1_MAX_ADDR : in std_logic_vector(23 downto 0);

signal RD1_LENGTH : in std_logic_vector(8 downto 0);

signal RD1_LOAD : in std_logic.

signal RD1_LOAD

: in std logic;

signal RD1 CLK

: out std_logic;

: out std_logic_vector( 8 downto 0);

signal RD1 EMPTY

signal RD1_USE

223 end component;

224

226 component SEG7_LUT_8 is port (

signal oSEG0, oSEG1, oSEG2, oSEG3, oSEG4, oSEG5, oSEG6, oSEG7

: out std_logic_vector( 6 downto 0);

signal iDIG : in std logic vector(31 downto 0) );

230 end component;

232 component I2C_CCD_Config is port (

signal iCLK : IN std_logic;

signal iRST_N : IN std_logic;

234

signal iExposure : IN std_logic_vector(15 downto 0);

236

signal I2C_SCLK : OUT std_logic;

signal I2C_SDAT : INOUT std_logic );

238 end component;

240 component Mirror_Col is port ( -- Input Side

iCCD_R : in std_logic_vector(9 downto 0);

iCCD_G : in std_logic_vector(9 downto 0);

iCCD_B : in std_logic_vector(9 downto 0);

iCCD_DVAL : in std_logic;

iCCD_PIXCLK : in std_logic;

iRST_N : in std_logic;

244

247

-- Output Side

oCCD_R : out std_logic_vector(9 downto 0);

oCCD G

: out std_logic_vector(9 downto 0);

oCCD_B

250

: out std_logic_vector(9 downto 0);

oCCD_DVAL : out std_logic

```

```

252 end component;

254

255 -- CCD

256 signal CCD DATA: std logic vector( 9 downto 0);

257 signal CCD SDAT : std logic;

258 signal CCD_SCLK : std_logic;

259 signal CCD_FLASH : std_logic;

260 signal CCD_FVAL : std_logic;

261 signal CCD LVAL : std logic;

262 signal CCD PIXCLK : std logic;

263 signal CCD MCLK : std logic; -- CCD Master Clock

264 signal Read_DATA1 : std_logic_vector(15 downto 0);

265 signal Read_DATA2 : std_logic_vector(15 downto 0);

266 signal VGA_CTRL_CLK : std_logic;

267 signal AUD CTRL CLK : std logic;

268 signal mCCD_DATA : std_logic_vector( 9 downto 0);

269 signal mCCD DVAL : std logic;

270 signal mCCD_DVAL_d : std_logic;

271 signal X_Cont : std_logic_vector(10 downto 0);

272 signal Y_Cont : std_logic_vector(10 downto 0);

273 signal X_ADDR : std_logic_vector(9 downto 0);

274 signal Frame_Cont : std_logic_vector(31 downto 0);

275 signal mCCD_R : std_logic_vector(9 downto 0);

276 signal mCCD_G : std_logic_vector(9 downto 0);

277 signal mCCD_B : std_logic_vector(9 downto 0);

278 signal DLY_RST_0 : std_logic;

279 signal DLY_RST_1 : std_logic;

280 signal DLY_RST_2 : std_logic;

281 signal Read : std_logic;

282 signal rCCD_DATA : std_logic_vector(9 downto 0);

283 signal rCCD_LVAL : std_logic;

284 signal rCCD_FVAL : std_logic;

285 signal sCCD_R : std_logic_vector(9 downto 0);

286 signal sCCD_G : std_logic_vector(9 downto 0);

287 signal sCCD_B : std_logic_vector(9 downto 0);

288 signal

sCCD_DVAL : std_logic;

289 signal mNewFrame : std_logic;

290 signal clk : std_logic;

292

signal counter : std_logic_vector(15 downto 0);

signal reset_n : std_logic;

294

signal Count0, Count1, Count2, Count3, Count4, Count5, Count6, Count7 : st

d_logic_vector(31 downto 0);

signal min0, min1, min2, min3, min4, min5, min6, min7 : std_logic_vector(3

1 downto 0);

signal max0, max1, max2, max3, max4, max5, max6, max7 : std logic vector(3

1 downto 0);

298 begin

300 clk <= CLOCK_50;

301 -- LEDR(17) <= '1';

302 -- LEDR(16) <= '1';

process (CLOCK_50)

304

begin

```

```

if CLOCK_50'event and CLOCK_50 = '1' then

if counter = x"ffff" then

reset n <= '1';

else

reset n <= '0';

counter <= counter + 1;</pre>

end if;

end if;

314

end process;

nios : nios_system port map (

=> CLOCK 50,

clk

318

reset n

=> reset n,

Count0_to_the_communication_0 => Count0,

Count1 to the communication 0 => Count1,

Count2 to the communication 0 => Count2,

Count3 to the communication 0 => Count3,

Count4_to_the_communication_0 => Count4,

324

Count5_to_the_communication_0 => Count5,

Count6_to_the_communication_0 => Count6,

Count7_to_the_communication_0 => Count7,

min0 from the communication 0 => min0,

max0_from_the_communication_0 => max0,

min1_from_the_communication_0 => min1,

max1_from_the_communication_0 => max1,

min2_from_the_communication_0 => min2,

max2_from_the_communication_0 => max2,

min3_from_the_communication_0 => min3,

334

max3_from_the_communication_0 => max3,

min4_from_the_communication_0 => min4,

max4_from_the_communication_0 => max4,

min5_from_the_communication_0 => min5,

max5_from_the_communication_0 => max5,

min6_from_the_communication_0 => min6,

max6 from the communication 0 => max6,

min7 from the communication 0 => min7,

max7_from_the_communication_0 => max7,

343

344

leds_from_the_leds

=> LEDR(15 downto 0),

345

SRAM_ADDR_from_the_sram

=> SRAM_ADDR,

SRAM_CE_N_from_the_sram

=> SRAM_CE_N,

347

SRAM_DQ_to_and_from_the_sram => SRAM_DQ,

348

SRAM_LB_N_from_the_sram

=> SRAM_LB_N,

SRAM_OE_N_from_the_sram

=> SRAM_OE_N,

SRAM_UB_N_from_the_sram

=> SRAM_UB_N,

SRAM_WE_N_from_the_sram

=> SRAM_WE_N

);

354

--histo

h0: histo port map(clk,mCCD_R,mCCD_G,mCCD_B,mCCD_DVAL_d,mNewFrame,m

in0, max0, Count0);

h1: histo port map(clk,mCCD_R,mCCD_G,mCCD_B,mCCD_DVAL_d,mNewFrame,m

in1,max1,Count1);

h2: histo port map(clk,mCCD_R,mCCD_G,mCCD_B,mCCD_DVAL_d,mNewFrame,m

in2, max2, Count2);

h3: histo port map(clk,mCCD_R,mCCD_G,mCCD_B,mCCD_DVAL_d,mNewFrame,m

```

```

in3,max3,Count3);

h4: histo port map(clk, mCCD_R, mCCD_G, mCCD_B, mCCD_DVAL_d, mNewFrame, m

in4, max4, Count4);

h5: histo port map(clk, mCCD R, mCCD G, mCCD B, mCCD DVAL d, mNewFrame, m

in5, max5, Count5);

h6: histo port map(clk, mCCD R, mCCD G, mCCD B, mCCD DVAL d, mNewFrame, m

in6,max6,Count6);

h7: histo port map(clk,mCCD_R,mCCD_G,mCCD_B,mCCD_DVAL_d,mNewFrame,m

in7,max7,Count7);

364

CCD DATA(0) \leftarrow GPIO 1(0);

CCD DATA(1) <= GPIO 1(1);</pre>

CCD_DATA(2) <= GPIO_1(5);</pre>

CCD_DATA(3) <= GPIO_1(3);</pre>

CCD_DATA(4) \leftarrow GPIO_1(2);

CCD DATA(5) \leftarrow GPIO 1(4);

CCD DATA(6) \leftarrow GPIO 1(6);

372

CCD DATA(7) \leftarrow GPIO 1(7);

CCD DATA(8) <= GPIO 1(8);

374

CCD_DATA(9) <= GPIO_1(9);</pre>

GPIO_1(11) <= CCD_MCLK;</pre>

376 -- GPIO 1(15) <= CCD SDAT;

377 -- GPIO_1(14) <= CCD_SCLK;

378

CCD_FVAL

<= GPIO_1(13);

CCD_LVAL <= GPIO_1(12);</pre>

379

CCD_PIXCLK <= GPIO_1(10);</pre>

<= SW;

LEDR

<= Y_Cont(8 downto 0);

LEDG

VGA_CTRL_CLK<= CCD_MCLK;

384

--halve module

process (CLOCK_50)

begin

if CLOCK_50'event and CLOCK_50 = '1' then

CCD MCLK <= not CCD MCLK;

end if;

end process;

394

process (CCD_PIXCLK)

begin

if CCD_PIXCLK'event and CCD_PIXCLK='1' then

rCCD_DATA <= CCD_DATA;</pre>

<= CCD_LVAL;

<= CCD_FVAL;</pre>

398

rCCD_LVAL

rCCD_FVAL

400

end if;

end process;

403

u1 : VGA Controller port map(

404

iRed => Read DATA2(9 downto 0),

iGreen => Read_DATA1(14 downto 10)&Read_DAT

A2(14 downto 10),

iBlue => Read_DATA1(9 downto 0),

406

407

oRequest => Read,

-- VGA Side

oVGA_R => VGA_R,

410

oVGA_G => VGA_G,

```

```

Date: May 09, 2007

lab5.vhd

Project: lab5

411

oVGA_B => VGA_B,

412

oVGA_H_SYNC => VGA_HS,

413

oVGA V SYNC => VGA VS,

414

oVGA SYNC => VGA SYNC,

415

oVGA BLANK => VGA BLANK,

416

OVGA CLOCK => VGA CLK,

417

-- Control Signal

418

iCLK => VGA_CTRL_CLK,

419

iRST_N => DLY_RST_2 );

420

421

u2: Reset Delay

port map(

422

iCLK => CLOCK 50,

423

iRST => KEY(0),

oRST_0 => DLY_RST_0,

424

425

oRST_1 => DLY_RST_1,

oRST_2 => DLY_RST_2 );

426

427

428

u3: CCD Capture

port map(

429

oDATA => mCCD_DATA,

430

oDVAL => mCCD_DVAL,

431

oX_Cont => X_Cont,

oY_Cont => Y_Cont,

432

433

oFrame_Cont => Frame_Cont,

434

oNewFrame => mNewFrame,

435

iDATA => rCCD_DATA,

436

iFVAL => rCCD_FVAL,

437

iLVAL => rCCD_LVAL,

438

iSTART => '1',

439

iEND => not(KEY(2)),

440

iCLK => CCD_PIXCLK,

441

iRST => DLY_RST_1 );

442

443

u4: RAW2RGB

port map(

444

oRed => mCCD_R,

445

oGreen => mCCD_G,

446

oBlue => mCCD_B,

447

oDVAL => mCCD_DVAL_d,

448

iX_Cont => X_Cont,

iY_Cont => Y_Cont,

449

450

iDATA => mCCD_DATA,

451

iDVAL => mCCD_DVAL,

452

iCLK => CCD_PIXCLK,

453

iRST => DLY_RST_1 );

454

455

u5: SEG7_LUT_8

port map(

456

oSEG0 => HEX0, oSEG1 => HEX1,

457

oSEG2 => HEX2, oSEG3 => HEX3,

oSEG4 => HEX4, oSEG5 => HEX5,

458

459

oSEG6 => HEX6, oSEG7 => HEX7,

460

iDIG => Frame Cont );

461

u6: Sdram_Control_4Port port map(

-- HOST Side

464

REF_CLK => CLOCK_50,

RESET_N => '1',

465

466

-- FIFO Write Side 1

467

'0'&sCCD_G(9 downto 5)&sCCD

WR1_DATA =>

```

Page 9 of 11

```

_B(9 downto 0),

WR1 => sCCD_DVAL,

469

WR1 ADDR => "00000000000000000000000000",

470

WR1 MAX ADDR => "00000101000000000000000",

471

WR1 LENGTH => "100000000",

472

WR1 LOAD => not(DLY RST 0),

473

WR1_CLK => CCD_PIXCLK,

474

-- FIFO Write Side 2

475

WR2_DATA => '0'&sCCD_G(4 downto 0)&sCCD_R(9

downto 0),

476

WR2 => sCCD DVAL,

477

WR2 ADDR => "000100000000000000000000",

478

WR2 MAX ADDR => "00010101000000000000000",

479

WR2 LENGTH => "100000000",

WR2_LOAD => not(DLY_RST_0),

480

WR2 CLK => CCD PIXCLK,

-- FIFO Read Side 1

RD1 DATA => Read DATA1,

484

RD1 => Read,

RD1 ADDR => "0000000001010000000000",

485

486

RD1_MAX_ADDR => "0000000000000111110000",

RD1 LENGTH => "100000000",

487

RD1_LOAD => not(DLY_RST_0),

489

RD1_CLK => VGA_CTRL_CLK,

490

-- FIFO Read Side 2

491

RD2_DATA => Read_DATA2,

RD2 => Read,

492

RD2_ADDR => "0001000001010000000000",

493

494

RD2_MAX_ADDR => "00010100110110000000000",

495

RD2_LENGTH => "100000000",

496

RD2_LOAD => not(DLY_RST_0),

497

RD2_CLK => VGA_CTRL_CLK,

498

-- SDRAM Side

499

SA => DRAM_ADDR,

BA(1) = > DRAM BA 1,

BA(0) => DRAM BA 0,

CS_N => DRAM_CS_N,

CKE => DRAM_CKE,

RAS_N => DRAM_RAS_N,

CAS_N => DRAM_CAS_N,

WE_N => DRAM_WE_N,

DQ => DRAM_DQ,

DQM(1) => DRAM_UDQM,

DQM(0) => DRAM_LDQM,

SDR_CLK => DRAM_CLK );

512

u7: I2C CCD Config

port map (

iCLK => CLOCK 50,

514

iRST N => KEY(1),

iExposure => SW(15 downto 0),

I2C\_SCLK \Rightarrow GPIO\_1(14),

I2C_SDAT => GPIO_1(15) );

518

519

u8: Mirror Col

port map( -- Input Side

iCCD R => mCCD R,

iCCD_G => mCCD_G,

iCCD_B => mCCD_B,

```

| Date: May 09, 2007 | lab5.vhd                                                                                                                                                                                             | Project: lab5 |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 528<br>529         | <pre>iCCD_DVAL =&gt; mCCD_DVAL_d, iCCD_PIXCLK =&gt; CCD_PIXCLK, iRST_N =&gt; DLY_RST_1, Output Side oCCD_R =&gt; sCCD_R, oCCD_G =&gt; sCCD_G, oCCD_B =&gt; sCCD_B, oCCD_DVAL =&gt; sCCD_DVAL);</pre> |               |

```

1 library ieee;

2 use ieee.std_logic_1164.all;

3 use ieee.std logic arith.all;

4 use ieee.std logic unsigned.all;

8 entity histo is port (

9

clk

: in std_logic; --50MHz

: in std_logic_vector(9 downto 0);

: in std_logic_vector(9 downto 0);

12

: in std_logic_vector(9 downto 0);

new_pixel : in std_logic;

14

new_frame : in std_logic;

: in std_logic_vector(31 downto 0);

Min

: in std logic vector(31 downto 0);

Max

: out std_logic_vector(31 downto 0) );

count

18 end histo;

19

20 architecture rtl of histo is

22 signal zero : std logic;

23 signal counter, counter2 : std_logic_vector(31 downto 0);

24 signal RedMin,RedMax,GreenMin,GreenMax,BlueMin,BlueMax : std_logic_vect

or(9 downto 0);

25 begin

27

count <= counter2;</pre>

RedMin <= Min(29 downto 20);</pre>

GreenMin<= Min(19 downto 10);</pre>

BlueMin <= Min( 9 downto 0);

RedMax <= Max(29 downto 20);</pre>

GreenMax<= Max(19 downto 10);</pre>

BlueMax <= Max( 9 downto 0);</pre>

34

process (clk)

begin

if clk'event and clk='1' then

if new_frame='0' and zero='1' then

zero <='0';

40

41

counter <= "0000000000000000000000000000000000";

42

end if;

43

if new_frame='1' then

44

45

counter2 <= counter;</pre>

zero

<= ' 1 ' i

47

end if;

48

49

if new_pixel='1' then

if R >= RedMin and R<=RedMax and

G >= GreenMin and G<=GreenMax and

B >= BlueMin and B<=BlueMax then

counter <= counter+1;</pre>

end if;

54

end if;

end if;

```

Date: May 09, 2007 histo.vhd Project: lab5

end process;

58

59 end rtl;

Page 2 of 2 Revision: lab5

```

1 library ieee;

2 use ieee.std_logic_1164.all;

3 use ieee.std logic arith.all;

4 use ieee.std logic unsigned.all;

6 entity communication is

8

port (

9

: in std_logic;

avs_s1_clk

avs_s1_reset_n : in std_logic;

: in std logic;

avs s1 read

: in std_logic;

12

avs s1 write

avs_s1_chipselect : in std_logic;

14

avs_s1_address : in std_logic_vector(7 downto 0);

avs_s1_readdata : out std_logic_vector(31 downto 0);

avs_s1_writedata : in std_logic_vector(31 downto 0);

Count0, Count1, Count2, Count3, Count4, Count5, Count6, Count7

19

: in std_logic_vector(31 downto 0);

min0, max0, min1, max1, min2, max2, min3, max3, min4, max4, min5, max5, min6, ma

x6,min7,max7

21

: out std_logic_vector(31 downto 0)

);

23

24 end communication;

26 architecture rtl of communication is

27

28 signal reset : std_logic;

29 signal rmin0,rmax0,rmin1,rmax1,rmin2,rmax2,rmin3,rmax3,rmin4,rmax4,rmi

n5, rmax5, rmin6, rmax6, rmin7, rmax7

: std_logic_vector(31 downto 0);

31 signal rCount0,rCount1,rCount2,rCount3,rCount4,rCount5,rCount6,rCount7

: std_logic_vector(31 downto 0);

34 begin

35 reset<='0';

min0 <= rmin0; min1 <= rmin1; min2 <= rmin2; min3 <= rmin3; min4 <=

rmin4; min5 <= rmin5; min6 <= rmin6; min7 <= rmin7;</pre>

max0 <= rmax0; max1 <= rmax1; max2 <= rmax2; max3 <= rmax3; max4 <=

rmax4; max5 <= rmax5; max6 <= rmax6; max7 <= rmax7;</pre>

rCount0 <= Count0; rCount1 <= Count1; rCount2 <= Count2; rCount3 <=

Count3; rCount4 <= Count4; rCount5 <= Count5; rCount6 <= Count6; rCoun

t7 <= Count7;

40

process (avs_s1_clk)

41

begin

if avs s1 clk'event and avs s1 clk = '1' then

43

if reset = '1' then

44

avs_s1_readdata <= (others => '0');

45

else

46

if avs_s1_chipselect = '1' then

47

if avs s1 read = '1' then

avs_s1_address="000000000" then avs_s1_readdata

<=rCount0;

49

avs_s1_address="00000001" then avs_s1_readdata

elsif

<=rCount1;

```

```

1 module CCD_Capture( oDATA,

oDVAL,

oX Cont,

4

oY Cont,

5

oFrame Cont,

6

oNewFrame,

iDATA,

8

iFVAL,

9

iLVAL,

iSTART,

iEND,

iCLK,

iRST

);

14

15 input [9:0] iDATA;

16 input

17 input

iFVAL;

iLVAL;

iSTART;

18 input

19 input

iEND;

20 input

iCLK;

21 input

iRST;

22 output [9:0] oDATA;

23 output [10:0] oX_Cont;

24 output [10:0] oY_Cont;

25 output [31:0] oFrame_Cont;

26 output

oNewFrame;

oDVAL;

Pre_FVAL;

27 output

28 reg

29 reg

mCCD_FVAL;

30 reg

mCCD_LVAL;

mccd_Lval;

1 reg [9:0] mccd_Data;

1 reg [10:0] x_cont;

1 reg [10:0] y_cont;

1 reg [31:0] Frame_cont;

35 req

mSTART;

36 reg

rNewFrame;

38 assign oX_Cont = X_Cont;

39 assign oY_Cont = Y_Cont;

40 assign oFrame_Cont = Frame_Cont;

41 assign oDATA = mCCD_DATA;

42 assign oDVAL = mCCD_FVAL&mCCD_LVAL;

43 assign oNewFrame = rNewFrame;

44

45 always@(posedge iCLK or negedge iRST)

46 begin

47

if(!iRST)

48

mSTART <= 0;

49

else

begin

if(iSTART)

mSTART <= 1;

if(iEND)

54

mSTART <= 0;

end

56 end

```

```

58 always@(posedge iCLK or negedge iRST)

59 begin

if(!iRST)

begin

<= 0;

Pre FVAL

mCCD FVAL

<= 0;

64

mCCD_LVAL

<= 0;

65

mCCD_DATA

<= 0;

66

X_Cont

<= 0;

67

Y_Cont

<= 0;

end

else

begin

Pre_FVAL

<= iFVAL;

72

if( ({Pre_FVAL,iFVAL}==2'b01) && mSTART )

<= 1;

mCCD FVAL

74

else if({Pre_FVAL,iFVAL}==2'b10)

mCCD FVAL

<= 0;

<= iLVAL;

mCCD_LVAL

mCCD_DATA <= iDATA;</pre>

78

if(mCCD_FVAL)

begin

if (mCCD_LVAL)

begin

if(X_Cont<1279)</pre>

83

X_Cont <= X_Cont+1;</pre>

84

else

begin

X_Cont <= 0;</pre>

87

Y_Cont <= Y_Cont+1;</pre>

end

end

end

else

begin

X Cont <= 0;</pre>

Y_Cont <= 0;

94

end

end

97 end

99 always@(posedge iCLK or negedge iRST)

100 begin

if(!iRST)

Frame_Cont <= 0;</pre>

else

104

begin

if( ({Pre_FVAL,iFVAL}==2'b01) && mSTART )

Frame_Cont <= Frame_Cont+1;</pre>

108

rNewFrame <= 1'b1;</pre>

end

else

begin

rNewFrame <= 0;</pre>

end

114

end

```

CCD\_Capture.v Project: lab5

115 end 116 endmodule

Date: May 09, 2007

Page 3 of 3 Revision: lab5