# Hardware-Software Interfaces CSEE W4840

Prof. Stephen A. Edwards

Columbia University

Spring 2007

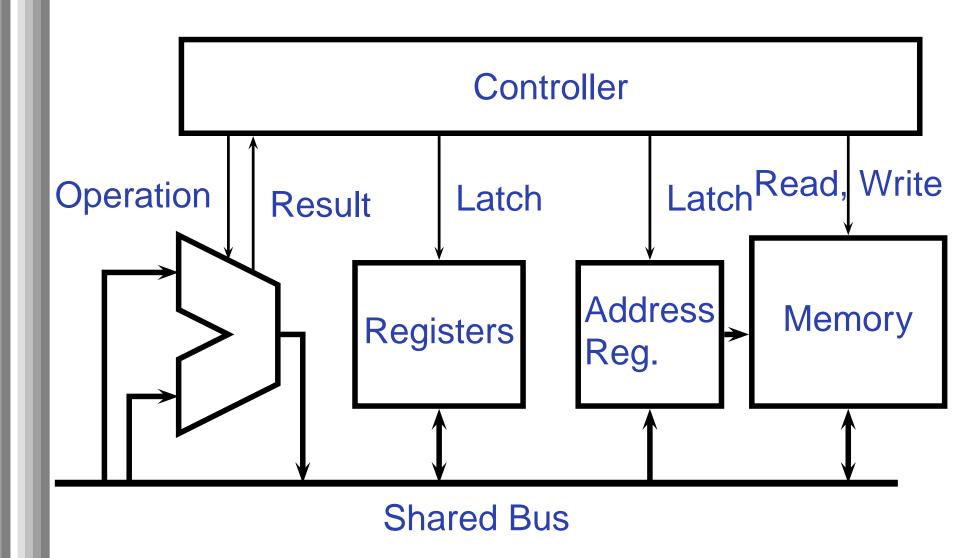

#### **Basic Processor Architecture**

## **Typical Processor System**

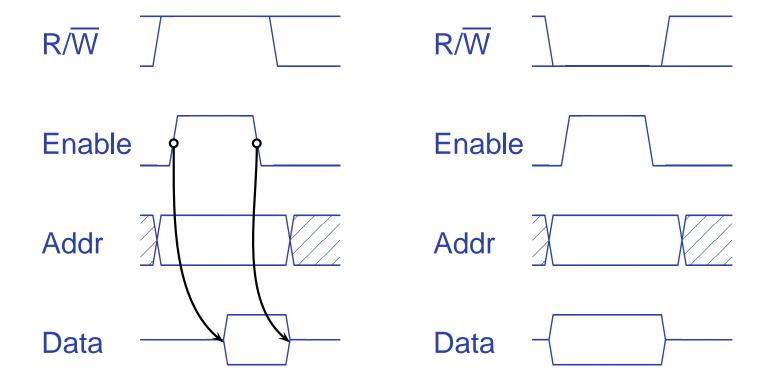

# Simple Bus Timing

#### **Read Cycle**

#### **Write Cycle**

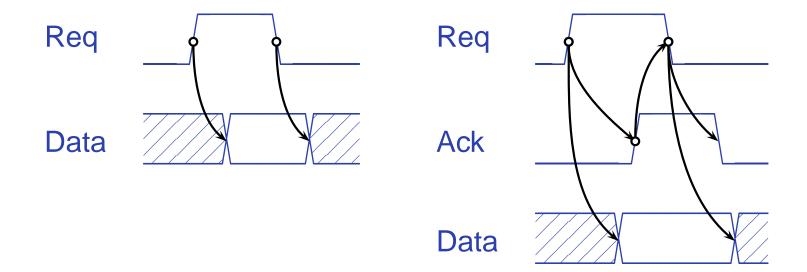

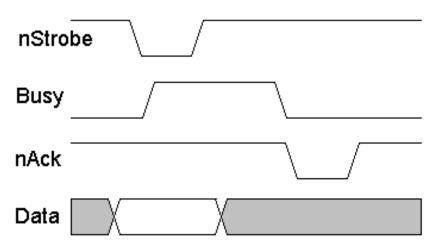

## Strobe vs. Handshake

#### **Strobe**

#### **Handshake**

#### 1982: The IBM PC

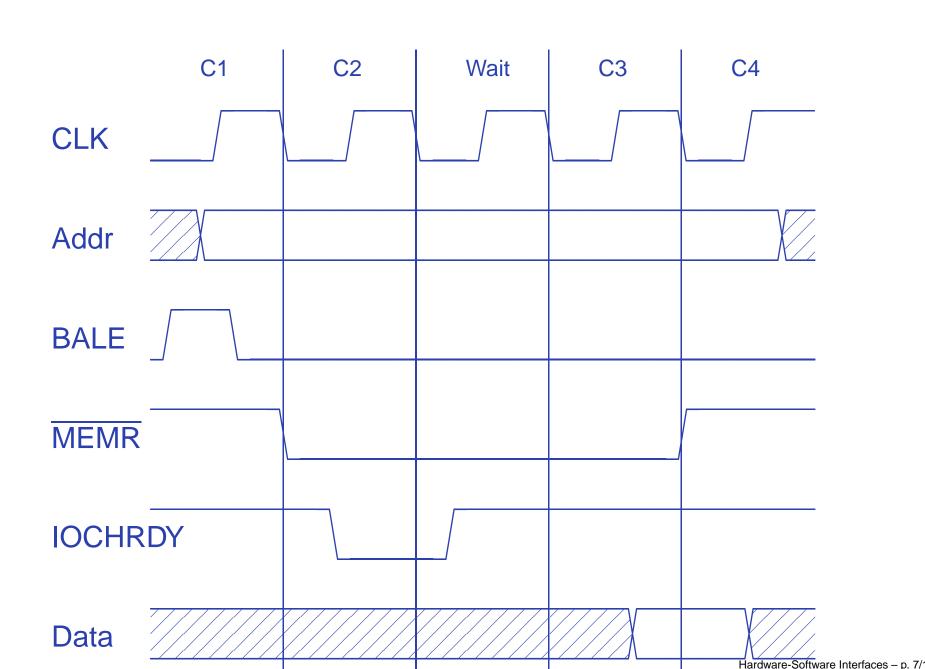

# The ISA Bus: Memory Read

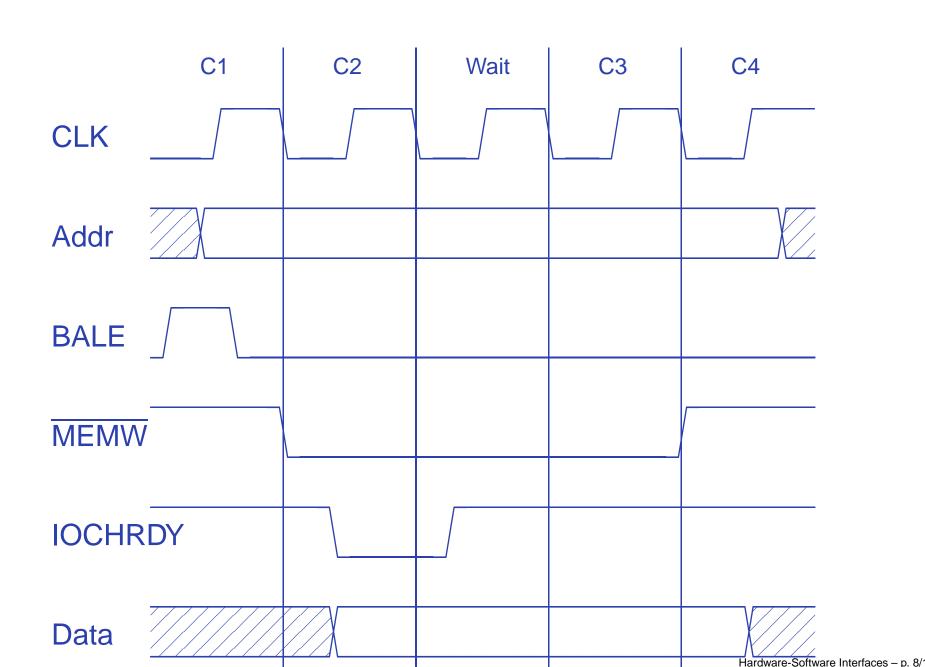

# The ISA Bus: Memory Write

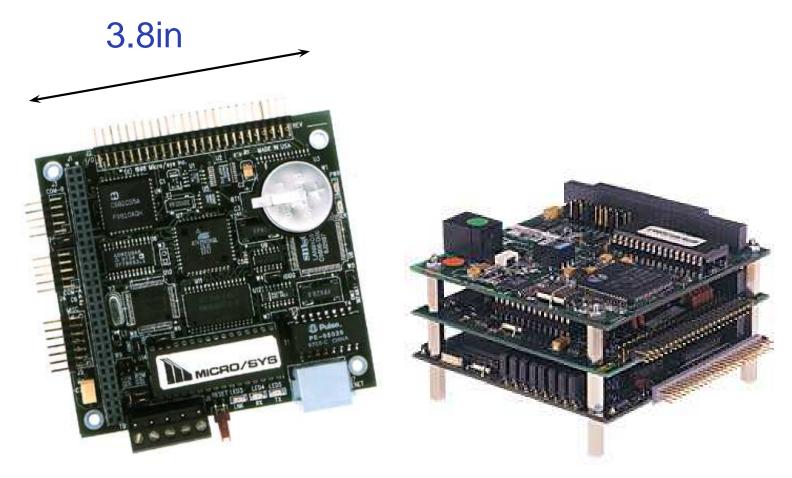

#### The PC/104 Form Factor: ISA Lives

Embedded System Legos. Stack 'em and go.

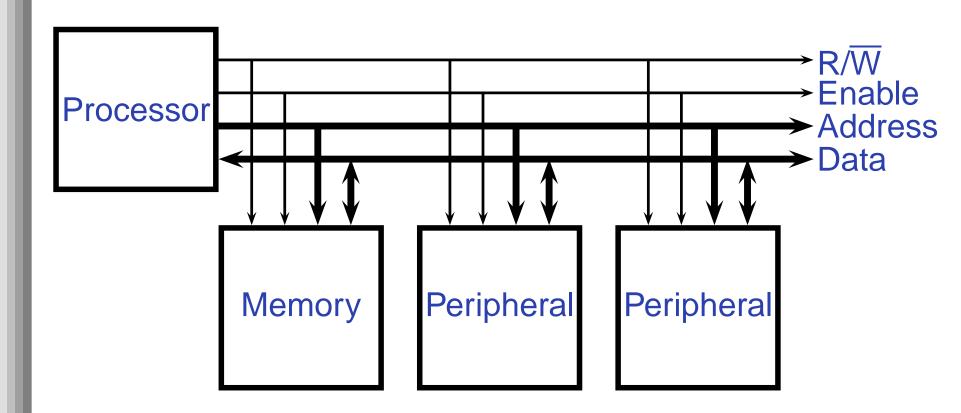

## **Memory-Mapped I/O**

- To a processor, everything is memory.

- Peripherals appear as magical memory locations.

- Status registers: when read, report state of peripheral

- Control registers: when written, change state of peripheral

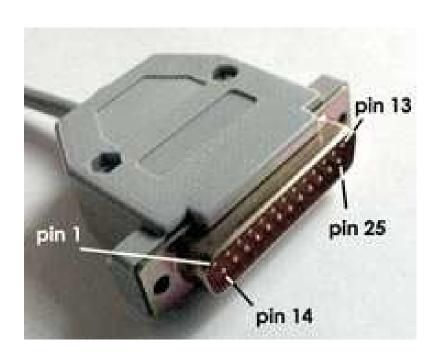

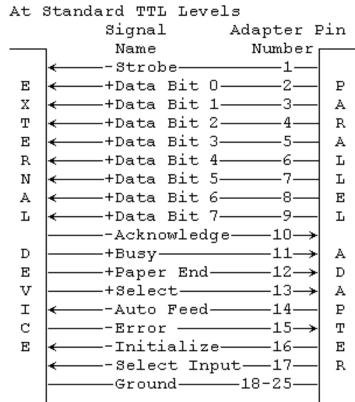

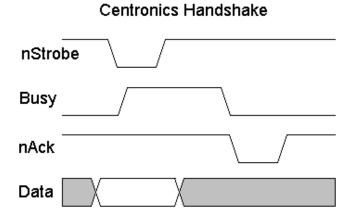

#### Typical Peripheral: PC Parallel Port

Centronics Handshake

## Parallel Port Registers

| D7   | D6  | D5    | D4  | D3  | D2   | D1   | D0     | 0x378 |

|------|-----|-------|-----|-----|------|------|--------|-------|

| Busy | Ack | Paper | Sel | Err |      |      |        | 0x379 |

|      |     |       |     | Sel | Init | Auto | Strobe | 0x37A |

- 1. Write Data

- 2. Assert Strobe

- 3. Wait for Busy to clear

- 4. Wait for Acknowledge

#### **A Parallel Port Driver**

```

#define DATA 0x378

#define STATUS 0x379

#define CONTROL 0x37A

#define NBSY 0x80

#define NACK 0x40

#define OUT 0x20

#define SEL 0x10

#define NERR 0x08

#define STROBE 0x01

#define INVERT (NBSY | NACK

SEL

NERR)

#define MASK

(NBSY | NACK | OUT | SEL

NERR)

#define NOT READY(x) ((inb(x)^INVERT)&MASK)

void write single character(char c) {

while (NOT READY(STATUS));

outb(DATA, c);

outb(CONTROL, control | STROBE); /* Assert STROBE */

outb(CONTROL, control ); /* Clear STROBE */

```

Hardware-Software Interfaces – p. 13/

## Interrupts and Polling

Two ways to get data from a peripheral:

- Polling: "Are we there yet?"

- Interrupts: Ringing Telephone

#### Interrupts

#### Basic idea:

- 1. Peripheral asserts a processor's interrupt input

- 2. Processor temporarily transfers control to interrupt service routine

- 3. ISR gathers data from peripheral and acknowledges interrupt

- 4. ISR returns control to previously-executing program

## **Many Different Interrupts**

What's a processor to do?

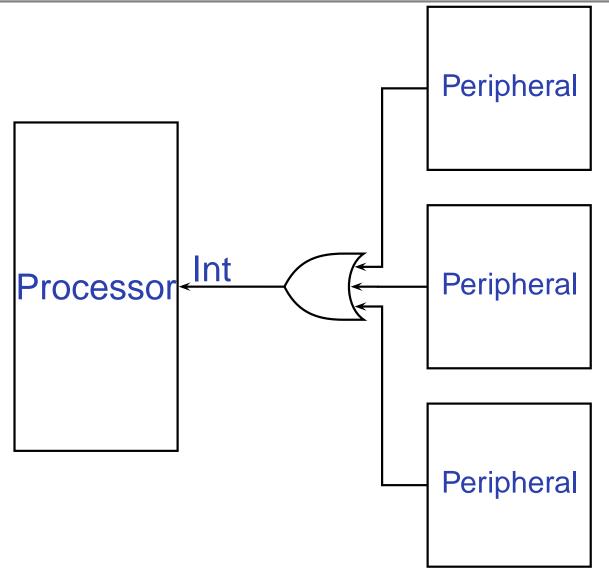

## Interrupt Polling

Processor receives interrupt ISR polls all potential interrupt sources

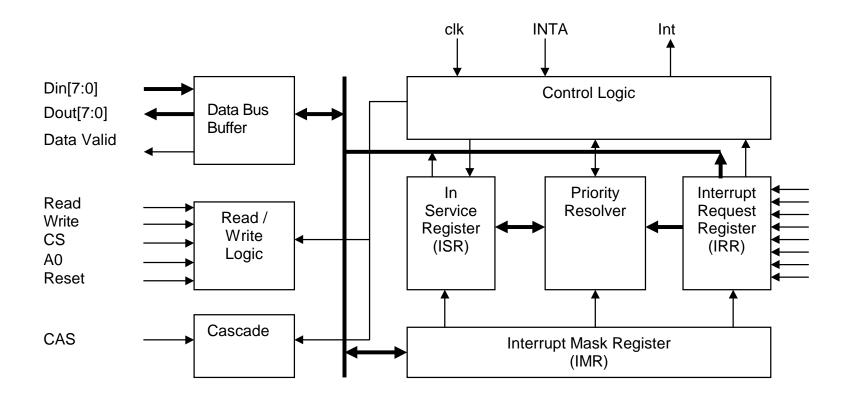

#### Intel 8259 PIC

Prioritizes incoming requests & notifies processor ISR reads 8-bit interrupt vector number of winner IBM PC/AT: two 8259s; became standard