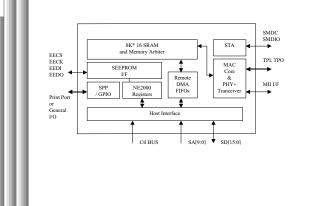

## AX88796 Ethernet Controller

iors, FPGAs, and ASICs - p. 29/3

.....

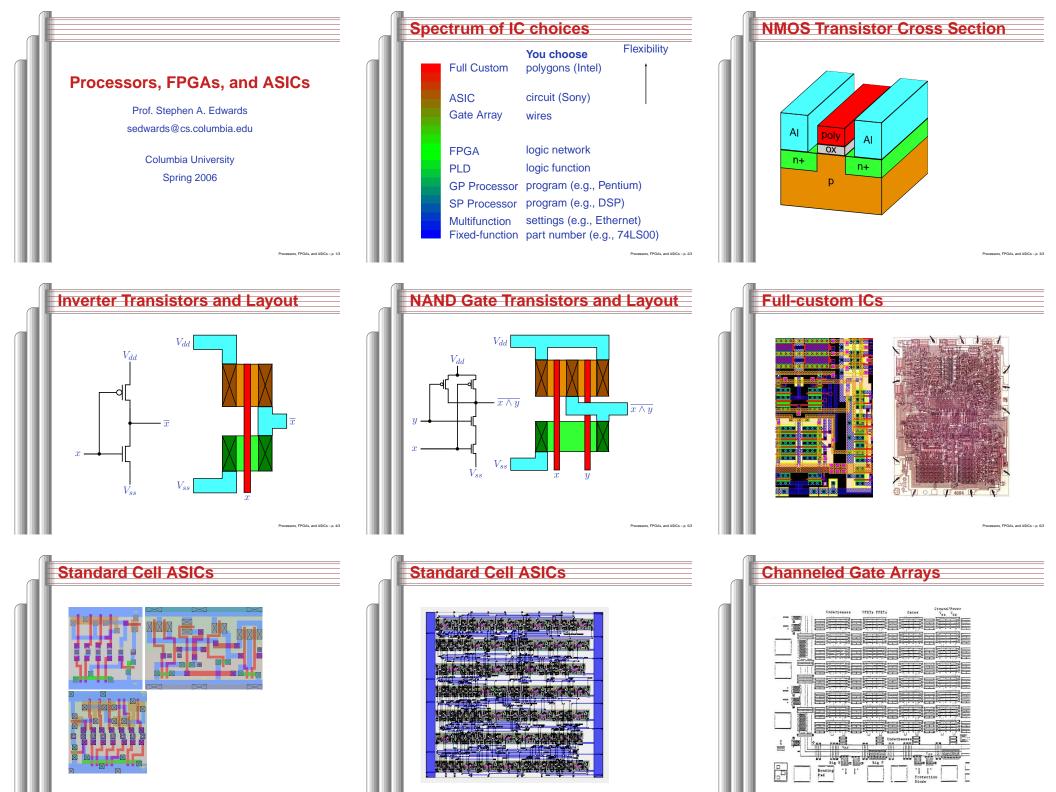

## Ethernet Controller Registers

| OFFSET | READ                          | WRITE                                       |  |  |  |

|--------|-------------------------------|---------------------------------------------|--|--|--|

| 00H    | Command Register              | Command Register                            |  |  |  |

|        | ( CR )                        | ( CR )                                      |  |  |  |

| 01H    | Page Start Register           | Page Start Register                         |  |  |  |

|        | (PSTART)                      | (PSTART)                                    |  |  |  |

| 02H    | Page Stop Register            | Page Stop Register                          |  |  |  |

|        | (PSTOP)                       | (PSTOP)                                     |  |  |  |

| 03H    | Boundary Pointer              | Boundary Pointer                            |  |  |  |

|        | (BNRY)                        | (BNRY)                                      |  |  |  |

| 04H    | Transmit Status Register      | Transmit Page Start Address                 |  |  |  |

|        | (TSR)                         | (TPSR)                                      |  |  |  |

| 05H    | Number of Collisions Register | Transmit Byte Count Register 0              |  |  |  |

|        | (NCR)                         | (TBCR0)                                     |  |  |  |

| 06H    | Current Page Register         | Transmit Byte Count Register 1              |  |  |  |

|        | (CPR)                         | (TBCR1)                                     |  |  |  |

| 07H    | Interrupt Status Register     | Interrupt Status Register                   |  |  |  |

|        | (ISR)                         | (ISR)                                       |  |  |  |

| 08H    | Current Remote DMA Address 0  | Remote Start Address Register 0             |  |  |  |

|        | (CRDA0)                       | (RSAR0)                                     |  |  |  |

| 09H    | Current Remote DMA Address 1  | Remote Start Address Register 1             |  |  |  |

|        | (CRDA1)                       | (RSAR1)                                     |  |  |  |

| 0AH    | Reserved                      | Remote Byte Count 0                         |  |  |  |

|        |                               | (RBCR0)                                     |  |  |  |

| 0BH    | Reserved                      | Remote Byte Count 1                         |  |  |  |

|        |                               | (RBCR1)                                     |  |  |  |

| 0CH    | Receive Status Register       | Receive Configuration Register Constant, FF |  |  |  |

|        | (RSR)                         | (RCR)                                       |  |  |  |

## <image><figure><figure>

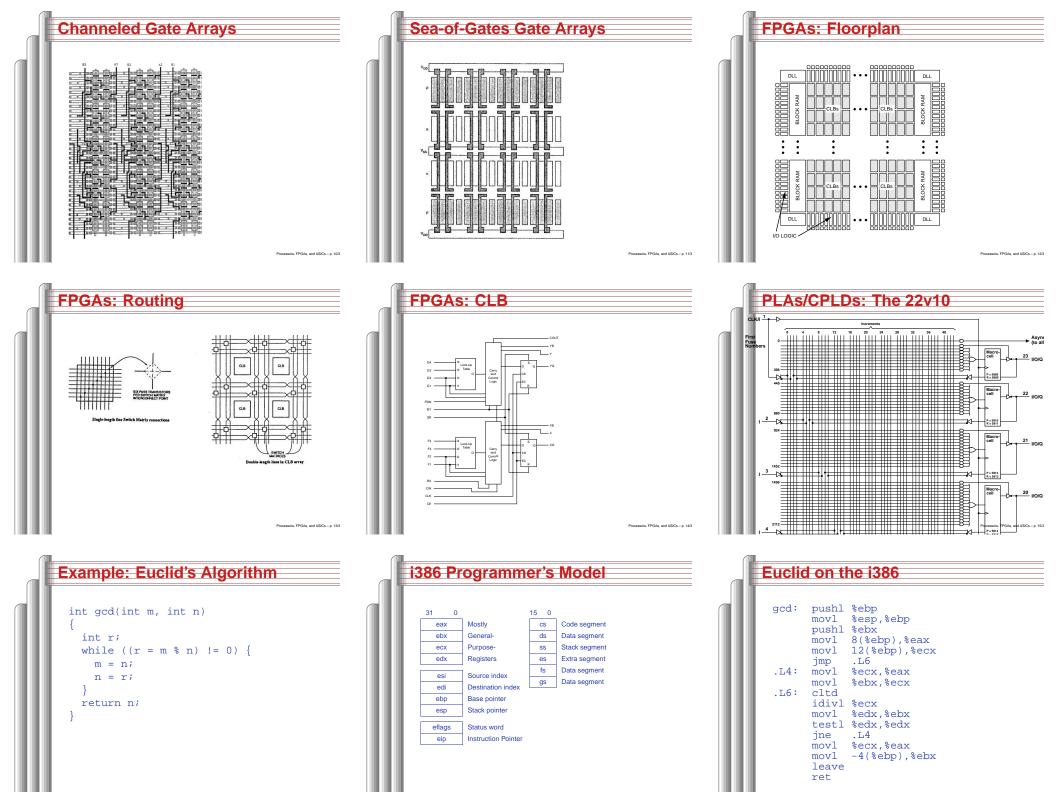

| REGISTERFUNCTION                    | SUB<br>ADDR.<br>(HEX) | D7     | D6     | D5     | 24     | D3     | D2     | D1     | DO             |

|-------------------------------------|-----------------------|--------|--------|--------|--------|--------|--------|--------|----------------|

| Chip version: register 00H          |                       |        |        |        |        |        |        |        |                |

| Chip version (read only)            | 00                    | ID07   | D06    | D05    | D04    | -      | -      | -      | -              |

| Video decoder: registers 01H t      | 281                   |        |        |        |        |        |        |        |                |

| FRONTHEND PART: REGISTERS 01H       | TO OSH                |        |        |        |        |        |        |        |                |

| Horizontal increment delay          | 01                    | (0     | 60     | (1)    | (1)    | DEL3   | DEL2   | DEL1   | DEL0           |

| Analog input control 1              | 02                    | FUSE1  | FUSED  | GUDL1  | GUDLO  | MCDE3  | MODE2  | MODE1  | MODE0          |

| Analog input control 2              | 03                    | (0     | HLNRS  | VBSL   | WPOFF  | HOLDG  | GAFIX  | G4428  | GA118          |

| Analog input control 3              | 04                    | GA17   | GAI16  | GAI15  | GAI14  | GAI13  | GAI12  | GAI11  | GA <b>1</b> 10 |

| Analog input control 4              | 05                    | GA427  | GA126  | GAL25  | GAL24  | GAE3   | GA122  | GAI21  | GA120          |

| DECCORR PART: REGISTERS 06H 1       | 2FH                   |        |        |        |        |        |        |        |                |

| Horizontalisyncistart               | 06                    | HS87   | HS86   | H9B5   | HSB4   | HSB3   | HSB2   | HS81   | HS80           |

| Horizontalisyncistop                | 07                    | HSS7   | HSS6   | HBS5   | HSS4   | HSS3   | HSS2   | HSS1   | HSSO           |

| Synccontrol                         | 08                    | ALFD   | FSEL   | FOET   | HTC1   | HTCO   | HPLL   | VNOII  | VNO0           |

| Luminancecontrol                    | 09                    | BYPS   | YCOMB  | LDEL.  | LUBW   | LUFIG  | LUFI2  | LUFI   | LUFI0          |

| Luminance brightness control        | 0A                    | DERI7  | DERIG  | DERIS  | DBRM4  | DERIC  | DERIZ  | DERM   | DERID          |

| Luminance contrast control          | 06                    | DCCIN/ | D00N6  | DCON5  | DCON4  | DOONS  | DOON/2 | DOONI  | 0000           |

| Chrominance saturation control      | 0C                    | DSAT7  | DSAT6  | DSAT5  | DSAT4  | D6AT3  | DSAT2  | DSAT1  | DSATO          |

| Chrominance hue control             | 00                    | HLEC7  | HJE06  | HLEC5  | HLEC4  | HUEC3  | HUEC2  | HJEC1  | HJEC0          |

| Chrominance control 1               | 0E                    | CDTO   | CSTD2  | CSTD1  | CSTDO  | DCVF   | FCTC   | (0)    | COOMB          |

| Chrominance gain comtrol            | 0F                    | ACGC   | CGAING | CGAIN5 | CGAIN4 | OGAINS | OGAIN2 | CGAINI | CGAINO         |

| Chrominance control 2               | 10                    | OFFU1  | OFFU0  | OFFV1  | OFF\0  | CHBW   | LCBW2  | LCBW1  | LCBM0          |

| Mode/dellay control                 | 11                    | 000    | RTP1   | HDBL1  | HDB.0  | RTF0   | YDEL2  | YDEL1  | YDELO          |

| RT signal control                   | 12                    | RTSE13 | RTSE12 | RTSE11 | RTSE10 | RTSECG | RTSE02 | RTSED1 | RTSECO         |

| RTX-portaulputconital               | 13                    | RICE   | XPHS   | XRNSI  | XFMS0  | HLSEL  | OFTS2  | OFTS1  | OFTSO          |

| AnalogiADC/compatibility<br>control | 14                    | CM99   | UPTOV  | AOBL1  | AO840  | XIOULE | OLDGB  | APOK1  | APCK0          |

| VGATE start, FID change             | 15                    | VSTA7  | VSTA6  | VSTA5  | VSTA4  | VSTAG  | VSTR2  | VSTA1  | VSTA0          |

| VGATEstop                           | 16                    | VST07  | VST06  | VST05  | VSTO4  | VSTCG  | VST02  | VST01  | VSTCO          |

| Miscelaneous/VGATE MSBs             | 17                    | LLCE   | LLC2E  | (1)    | (1)    | (1)    | VGPS   | VSTO8  | VSTA8          |

SAA7114H Registers, page 1 of 7 (!)

ors, FPGAs, and ASICs - p. 33